Altera CPRI IP Core User Manual

Page 171

Appendix C: CPRI Autorate Negotiation Testbench

C–9

Running the Autorate Negotiation Testbench

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

9. To compile and run the appropriate testbench for the DUT you generated in step

,

step

3

, or step

4

, perform one of the following sets of instructions, depending on

your target simulator:

■

To compile and run the testbench using the ModelSim or Aldec Riviera-PRO

simulator, start a simulator session and, in the simulator, type the following

commands:

cd

<

working

dir>/<variation>_testbench/altera_cpri/autorate_design/<vendor>_sim

r

do compile.tcl [<family> <HDL>] <vendor>

r

The <vendor> parameter has following valid values: mentor, aldec

The <family> and <HDL> parameters have the following valid values:

<family>: aiigx, aiigz, sivgx, civgx, av, avgt, avgz, cv, sv

<HDL>: vhd, vlg

■

To compile and run the testbench using the Synopsys VCS or Cadence NCSIM

simulator, type the following command sequence:

cd

<

working

dir>/<variation>_testbench/altera_cpri/autorate_design/<vendor>_sim

r

sh compile.sh [ –<family_code> <HDL_code>]

r

The <vendor> parameter designates the appropriate simulator vendor name,

synopsys

or

cadence

.

Table C–4

shows the valid values for the <family_code>

and <HDL_code> parameters.

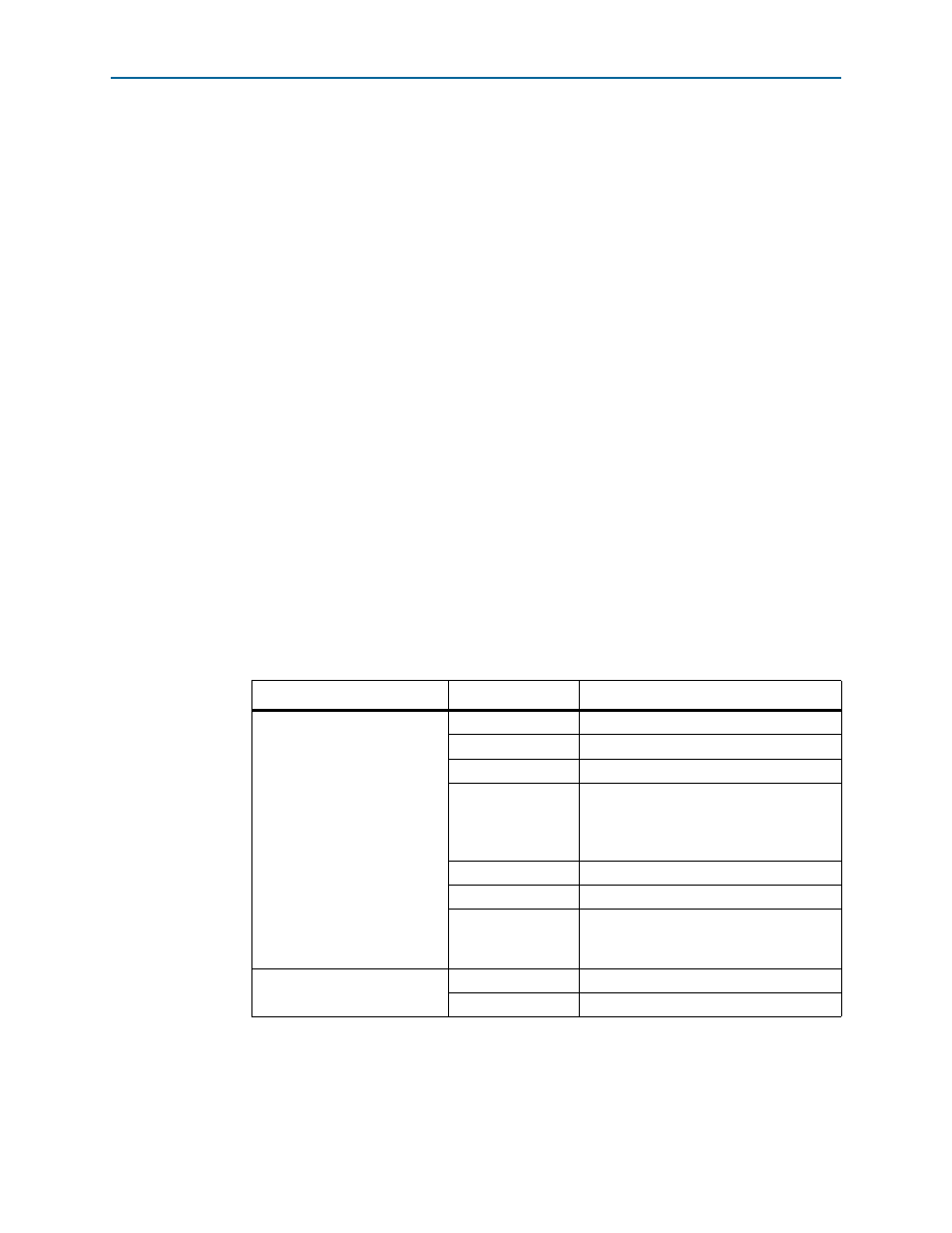

Table C–4. Parameter Values for Synopsys and Cadence Simulator Testbench Commands

Parameter

Value

Meaning

<family_code>

0

Stratix IV device family

3

Cyclone IV GX device family

4

Stratix V device family

5

Arria V (GX or GT) device family, if running

a testbench other than the testbench for

variations configured at a CPRI line rate of

9.8304 Gbps

6

Cyclone V GX device family

7

Arria V GZ device family

8

Arria V GT device family, if running the

testbench for variations configured at a

CPRI line rate of 9.8304 Gbps

<HDL_code>

0

VHDL

1

Verilog HDL