Altera CPRI IP Core User Manual

Page 123

Chapter 7: Software Interface

7–7

CPRI Protocol Interface Registers

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

For additional information about the

CPRI_HW_RESET

reset_detect

[4]

RO

Indicates that reset request has been detected in the incoming

stream on the CPRI link by the CPRI receiver.

1'h0

reset_hw_en

[3]

RW

Enable generation of reset request or acknowledge by CPRI

transmitter, as indicated by the

hw_reset_assert

input signal.

This enable bit has higher priority than the

reset_gen_en

bit; if

this enable bit is set, the

reset_gen_force

bit is ignored.

Note that when a CPRI RE slave detects a reset request in

incoming CPRI communication, and the

reset_hw_en

bit is

set, the user must assert the

hw_reset_assert

input signal to

the CPRI RE slave, to force it to send a reset acknowledge by

setting the reset bit in outgoing CPRI communication at

Z.130.0.

1'h0

reset_out_en

[2]

RW

Enable reset output.

1'h0

reset_gen_force

[1]

RW

Force generation of reset request or acknowledge by CPRI

transmitter.

1'h0

reset_gen_en

[0]

RW

Enable generation of reset request or acknowledge by CPRI

transmitter, as indicated by the

reset_gen_force

bit. This

enable bit has lower priority than the

reset_hw_en

bit; if the

reset_hw_en

bit is set, this bit and the

reset_gen_force

bit

are ignored.

1'h0

Note to

:

(1) This register field is a read-to-clear field. You must read the register twice to read the true value of the field after frame synchronization is

achieved. If you observe this bit asserted during link initialization, read the register again after link initialization to confirm any errors.

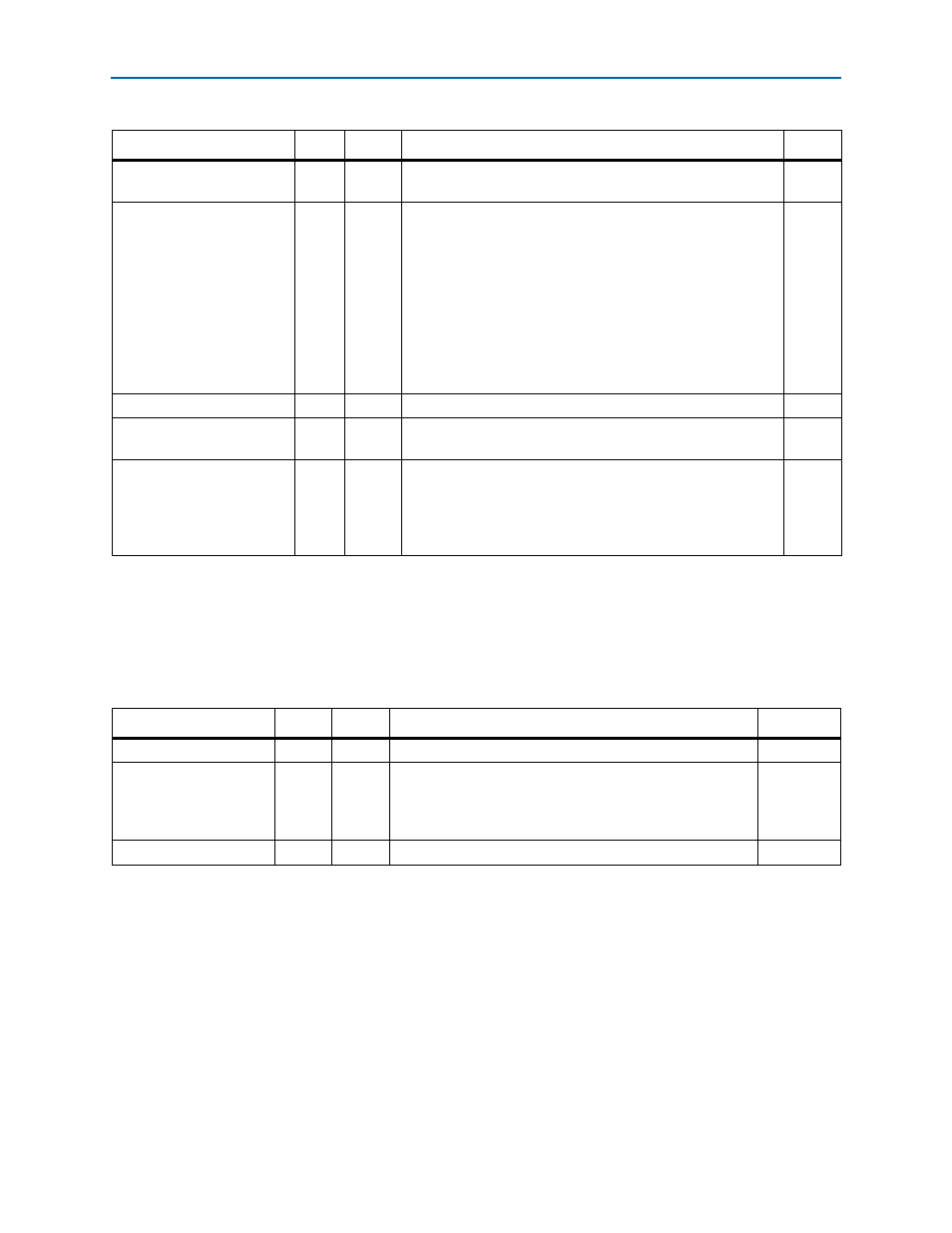

Table 7–12. CPRI_HW_RESET—Hardware Reset From Control Word—Offset: 0x20 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 7–13. CPRI_PHY_LOOP—Physical Layer Loopback Control—Offset: 0x24 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:5]

UR0

Reserved.

27'h0

loop_resync

[4]

RC

Indicates that reset resynchronization is detected. This bit is

typically set when the CPRI receiver clock and

cpri_clkout

have different frequencies, as measured in the physical layer

internal loopback path.

1’h0

RSRV

[3:1]

UR0

Reserved.

2'h0