Altera CPRI IP Core User Manual

Page 191

Appendix E: Delay Measurement and Calibration

E–13

Single-Hop Delay Measurement

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

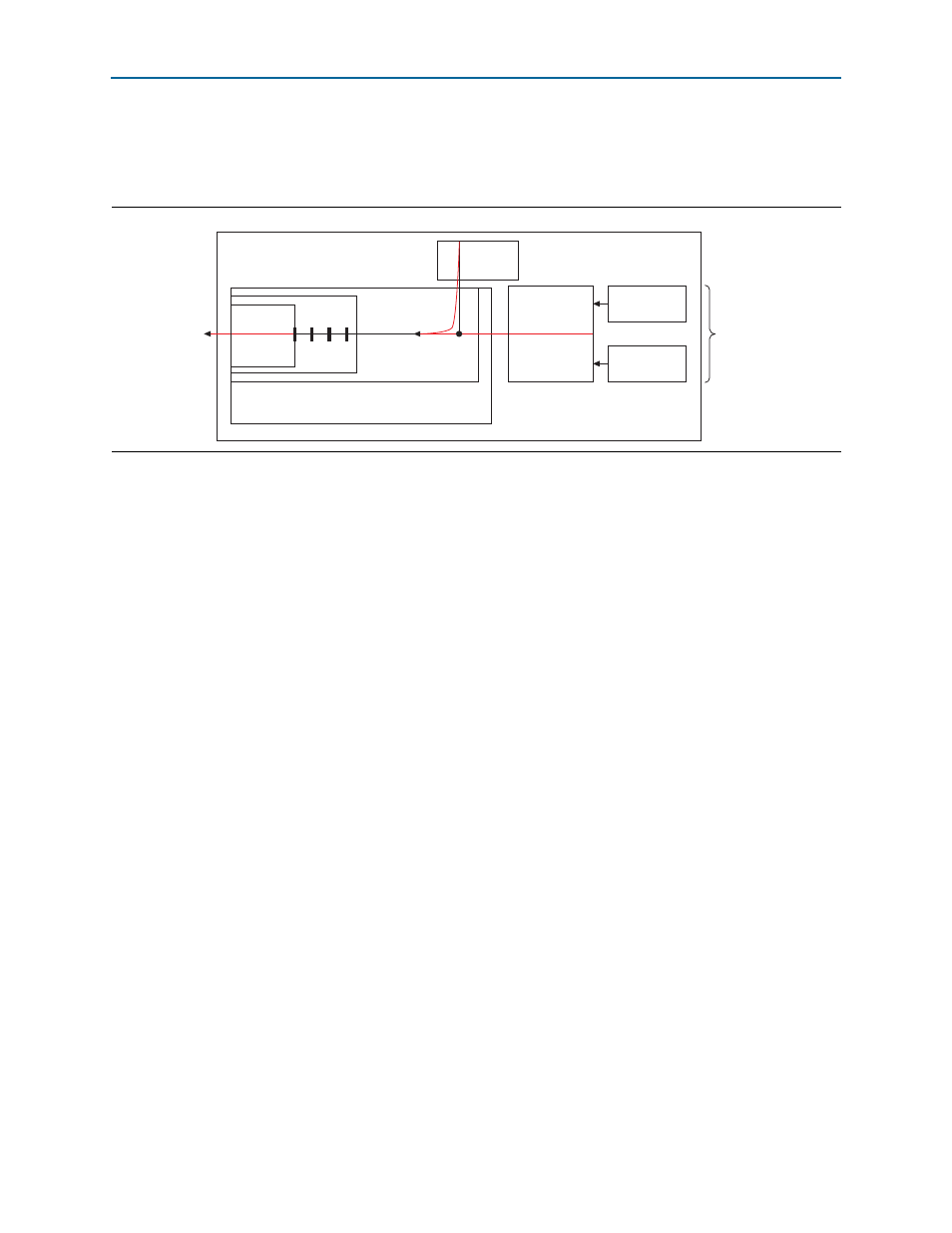

shows the Tx path delay components in all CPRI IP core variations except

those that target an Arria V GT device and are configured with the CPRI line rate of

9.8 Gbps. This figure shows the relation between the two Tx paths.

In the CPRI IP core the delay from the AUX interface has a fixed component and a

variable component. In the variations that do not target an Arria V GT device or that

are configured with a CPRI line rate other than 9.8 Gbps, the variable component

results from the Tx elastic buffer and the Tx bitslip delay compensation feature.

The Tx path delay from the AUX interface in most CPRI IP core variations comprises

the following delays:

1. Fixed delay from the AUX interface through the CPRI low-level transmitter to the

Tx elastic buffer. This delay depends on the device family and CPRI data rate. This

delay is the first component of

T_T4

in

Figure E–1 on page E–2

and in

. Refer to

“Fixed Tx Core Delay Component” on page E–14

.

2. Variable delay through the Tx elastic buffer, as well as the phase difference

between the core clock and the transceiver

tx_clkout

clock. The

section shows how to calculate the delay in the CPRI Tx

elastic buffer, which includes the phase difference delay.

3. Variable Tx bitslip delay in CPRI RE slaves. Refer to

4. Fixed delay from the Tx elastic buffer to the transceiver. This delay depends on the

device family and CPRI line rate. This delay is the second component of

T_T4

in

Figure E–1 on page E–2

and in

. Refer to

.

5. Link delay through the transceiver. This delay is

T_txv_TX

in

Table E–7 on

page E–16

.

Figure E–5. Tx Path Delay from AUX Interface or Through MAP Interface Block to CPRI Link in Most Variations

AxC IF 0

AxC IF n

...

AUX Interface

Data Channels

Transmitter

Transceiver

Transmitter

tx_dataout

Physical Layer

CPRI MAP

Interface Module

AUX

Module

(1)

(1)

(5)

(4) (3) (2)