Additional information, Document revision history – Altera CPRI IP Core User Manual

Page 213

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Additional Information

This chapter provides additional information about the document and Altera.

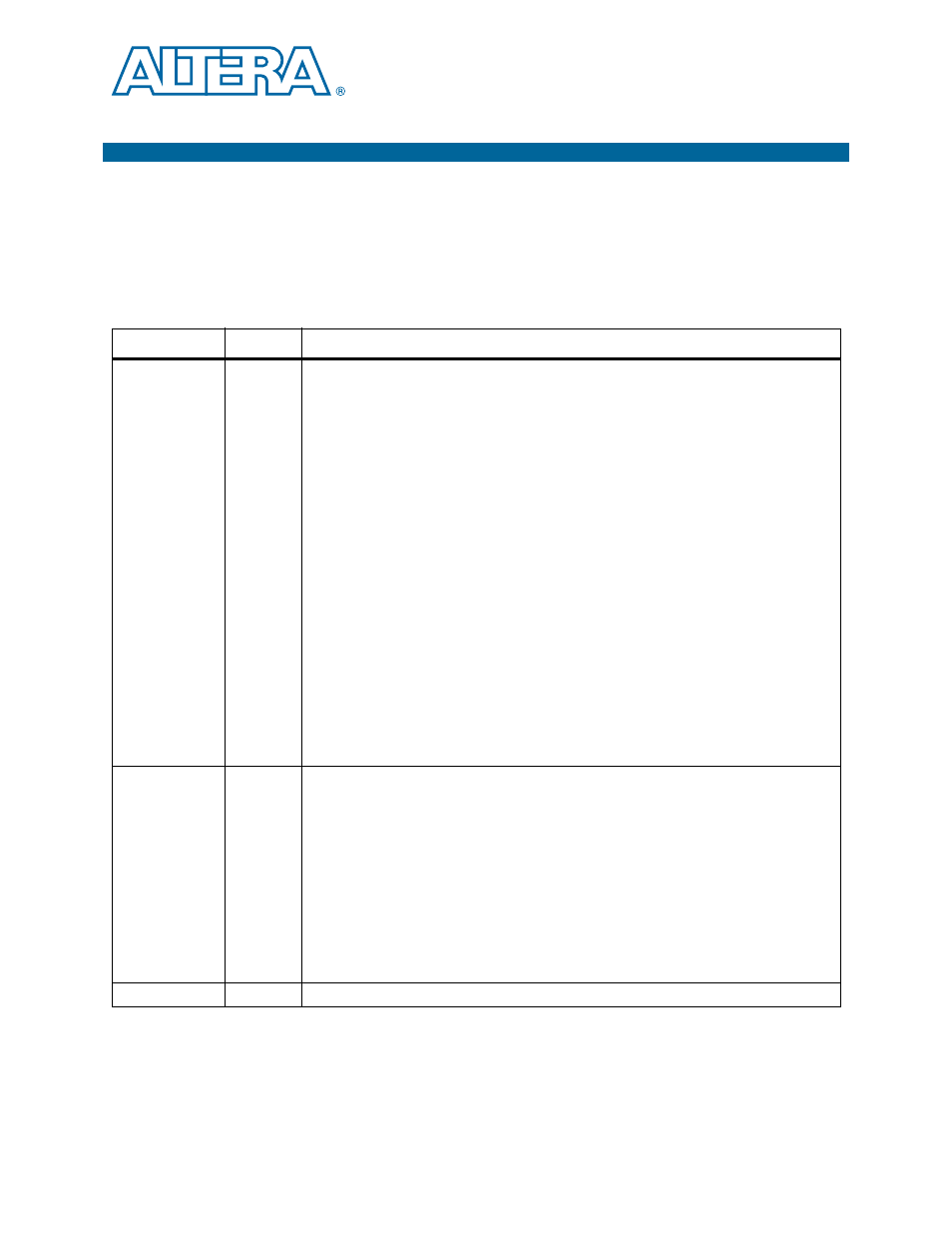

Document Revision History

The following table shows the revision history for this user guide.

.

Date

Version

Changes Made

December 2013

13.1

■

Updated latency numbers in

Appendix E, Delay Measurement and Calibration

for the

13.1 release.

■

Removed support for HardCopy IV GX devices.

■

Updated

Chapter 8, CPRI IP Core Demonstration Testbench

to describe the new

streamlined CPRI IP core demonstration testbench. This testbench exercises HDLC

functionality.

■

Added new appendix,

Appendix C, CPRI Autorate Negotiation Testbench

to describe the

legacy CPRI IP core autorate negotiation demonstration testbench.

■

Corrected description of

CPRI_MAP_CONFIG

register to add register field

map_tx_start_mode

in

. This register field is present in the

CPRI IP core starting with software release v11.1.

■

Updated

“Operation Mode Parameter” on page 3–2

, the introduction to

, and

“Dynamically Switching Clock Mode” on page 4–9

to clarify

that dynamic clock switching — switching between master and slave clocking modes —

is available only in CPRI IP core variations that target an Arria V device, a Cyclone V

device, or a Stratix V device.

■

Updated

to indicate the potential difficulty of achieving timing

closure on a 9.8304 Gbps CPRI IP core variation that targets an Arria V GT device.

■

redundant header information inside a table entry.

July 2013

13.0 SP1

■

Corrected latency numbers in

Appendix D, Delay Measurement and Calibration

and

reorganized this section.

■

Updated improved resource utilization performance numbers.

■

Added two new parameters: Include automatic round-trip delay calibration logic and

Include Vendor Specific Space (VSS) access through CPU interface.

■

Corrected Include MAC block setting for tb_altera_cpri_autorate_98G_phy testbench

in

Table 8–6 on page 8–9

.

■

Removed incorrect statement that Analog controls must be turned on for

altgx_reconfig

to connect correctly, in

“Supporting the Transceivers” on page 2–5

.

■

Corrected

pll_clkout

frequencies in Arria V GT devices in

Table 4–2 on page 4–10

.

March 2013

12.1 SP1

■

Updated latency numbers in

Appendix D, Delay Measurement and Calibration

.