Dynamically switching clock mode, Dynamically switching clock mode –9 – Altera CPRI IP Core User Manual

Page 41

Chapter 4: Functional Description

4–9

Clocking Structure

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

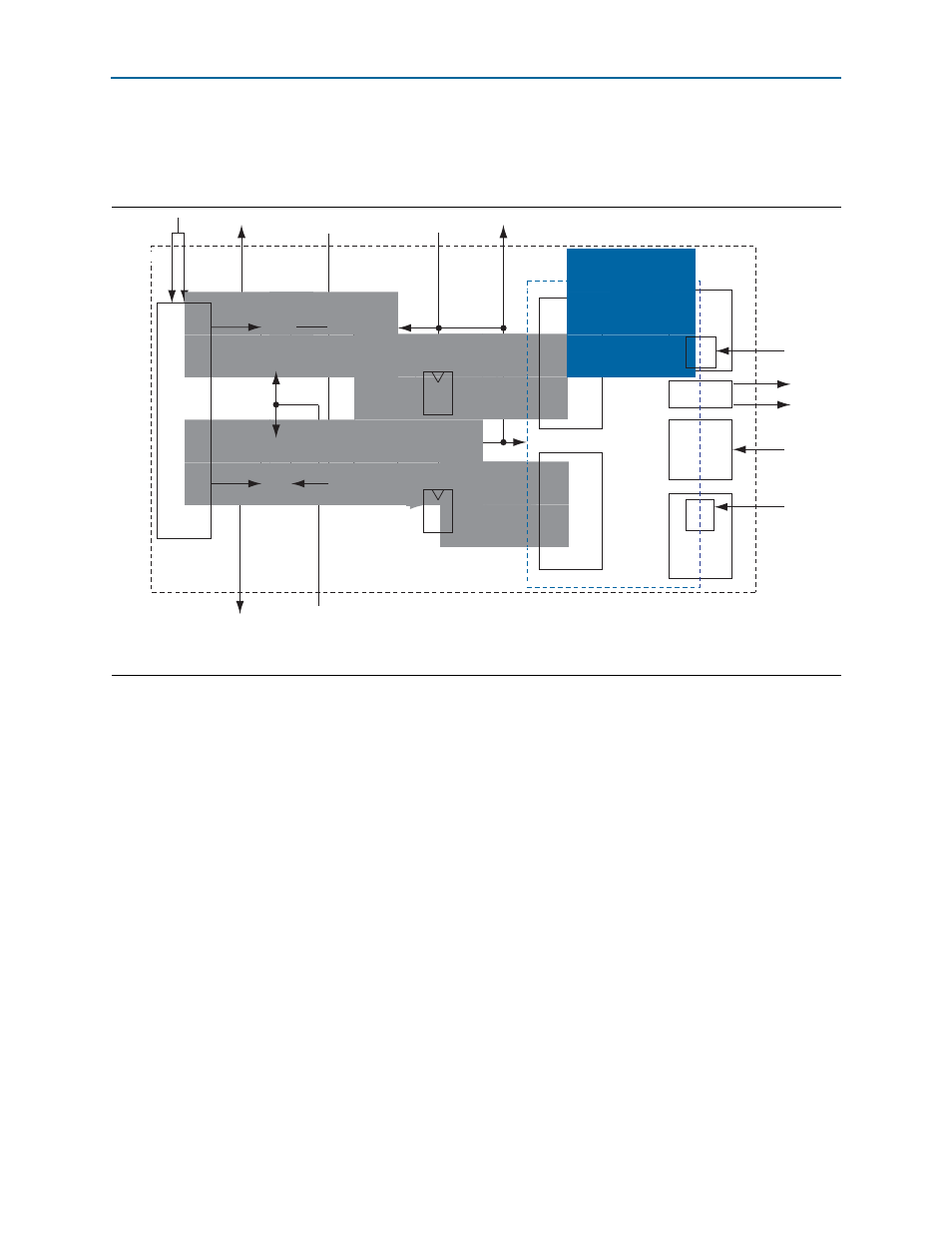

shows the clocking scheme for a CPRI IP core that targets an Arria V GT

device and is configured with a CPRI line rate of 9830.4 Mbps, configured or

programmed as an REC or RE master.

Dynamically Switching Clock Mode

The CPRI IP core supports dynamic clock mode switching in variations that target an

Arria V, Cyclone V, or Stratix V device, from master clock mode to slave clock mode

and from slave clock mode to master clock mode. The value you select for Operation

mode

in the CPRI parameter editor determines the clock mode in which the IP core is

configured initially. However, you can modify this value dynamically.

To switch the clock mode of your Arria V, Cyclone V, or Stratix V CPRI IP core,

perform the following steps:

1. Ensure your design supports the input clock connection requirements for the clock

mode to which you intend to switch the IP core.

2. Implement the clock connection requirements for the intended new clock mode by

switching the source that drives the

gxb_pll_inclk

signal. Refer to

Diagrams for the CPRI IP Core” on page 4–5

3. Write the new value to the

operation_mode

bit of the

CPRI_CONFIG

register. Refer to

for the appropriate value.

4. Wait until you observe successful CPRI link resynchronization. Refer to

Appendix A, Initialization Sequence

Figure 4–5. CPRI IP Core Master Clocking in Arria V GT 9.8 Gbps Variations

Notes to

(1) In master clocking mode, you must drive the

gxb_pll_inclk

and

gxb_refclk

input signals from a common source.

CPRI MegaCore Function

clk_ex_delay

pll_clkout

cpri_clkout

usr_clk

(245.76 MHz)

usr_pma_clk

(122.88 MHz)

gxb_refclk

gxb_pll_inclk tx_clkout

TX

Buffer

RX

Buffer

122.88 MHz

122.88 MHz

Soft

PCS

Soft

PCS

tx_clkout

rx_clkout

Transceiver

Native PHY

IP Core

CPRI TX

MII Interface

CPU

Interface

CPRI RX

FIFO

Buffer

cpu_clk

mapN_tx_clk

FIFO

Buffer

mapN_rx_clk

CPRI Rx

MAP

Interface

CPRI Tx

MAP

Interface

cpri_mii_txclk

cpri_mii_rxclk