Simulation files, Simulation files –3 – Altera CPRI IP Core User Manual

Page 19

Chapter 2: Getting Started

2–3

MegaWizard Plug-In Manager Design Flow

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

Generating your custom CPRI IP core variation creates a set of HDL files and

simulation models. You can now integrate your custom CPRI IP core variation in your

design, simulate, and compile.

Simulation Files

Generating a CPRI IP core creates an <instance_name>_sim directory with a

subdirectory for each of four different Altera-supported simulators for the current

software release. Each of the vendor-specific directories contains files and scripts to

simulate your CPRI IP core with that vendor’s simulation tools.

The <instance_name>_sim/altera_cpri directory contains the top-level simulation file

for your CPRI IP core.

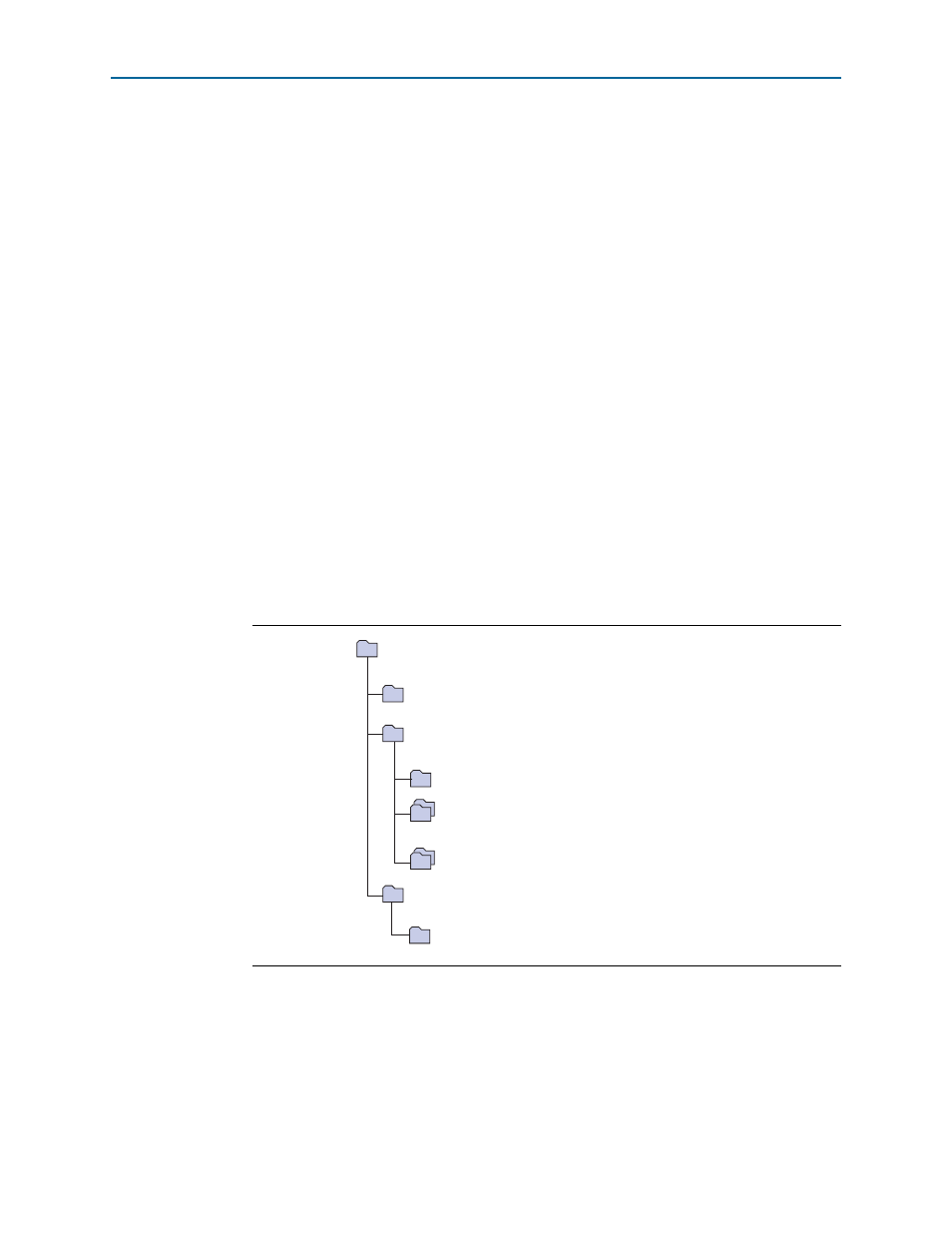

Generating a CPRI IP core creates a more complex directory structure for Arria V,

Cyclone V, and Stratix V variations than for variations that target other device

families, because the Arria V, Cyclone V, and Stratix V variations instantiate an Altera

Deterministic Latency PHY IP core or an Altera Native PHY IP core. In an Arria V,

Cyclone V, or Stratix V variation, your <instance_name>_sim directory contains

multiple subdirectories, one for each of the various components in the CPRI IP core, in

addition to the individual directories for vendors for four different simulators.

shows the directory structure of your CPRI IP core that contains a

Deterministic Latency PHY IP core and generates a testbench. Not all CPRI IP core

variations provide matching demonstration testbenches. For information about the

CPRI IP core variations that provide a testbench, refer to

The altera_xcvr_det_latency directory contains the files to simulate the Altera

Deterministic Latency PHY IP core that is generated as part of your CPRI IP core. It

also contains a mentor subdirectory with IEEE encrypted files to simulate the PHY IP

core efficiently.

Figure 2–2. Generated CPRI IP Core Directory Structure for Most 28-nm Variations

<working directory>

Vendor-specific directories contain simulation scripts

<instance name>_testbench

Contains the VHDL and System Verilog testbench simulation files

altera_cpri

Contains the lower-level testbench simulation files

altera_cpri_instance, altera_merlin_master_translator,

altera_merlin_slave_translator, altera_xcvr_det_latency

Contain the CPRI IP core instance lower-level simulation files

Quartus II project working directory

<instance name>_sim

CPRI IP core instance simulation files and scripts

<instance name>

CPRI IP core instance HDL files

altera_cpri

Contains the CPRI IP core instance top-level simulation file