Reset requirements, Reset requirements –11 – Altera CPRI IP Core User Manual

Page 43

Chapter 4: Functional Description

4–11

Reset Requirements

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

When you generate a CPRI IP core variation that targets an Arria II, Cyclone IV GX, or

Stratix IV GX device, you generate an ALTGX megafunction with specific default

settings. These default transceiver settings configure a transceiver that works

correctly with the CPRI IP core when the input

gxb_refclk

clock has the frequency

shown in

Table 4–2

. However, you can edit the ALTGX megafunction instance to

specify a different

gxb_refclk

frequency that is more convenient for your design, for

example, to enable you to use an existing clock in your system as the

gxb_refclk

reference clock.

When you generate a CPRI IP core variation that targets an Arria V, Cyclone V, or

Stratix V device, you generate an Altera Deterministic Latency PHY IP core or Altera

Native PHY IP core with specific default settings. However, you set the

gxb_refclk

frequency in the CPRI parameter editor. As described in

, for these target devices the CPRI parameter editor provides a list of potential

transceiver reference clock frequencies from which you select the frequency that is

most convenient for your design.

Reset Requirements

The CPRI IP core has multiple independent reset signals.To reset the CPRI IP core

completely, you must assert all the reset signals.

You can assert all reset signals asynchronously to any clock. However, each reset

signal must be asserted for at least one full clock period of a specific clock, and be

deasserted synchronously to the rising edge of that clock. For example, the CPU

interface reset signal,

cpu_reset

, must be deasserted on the rising edge of

cpu_clk

.

lists the reset signals and their corresponding clock domains.

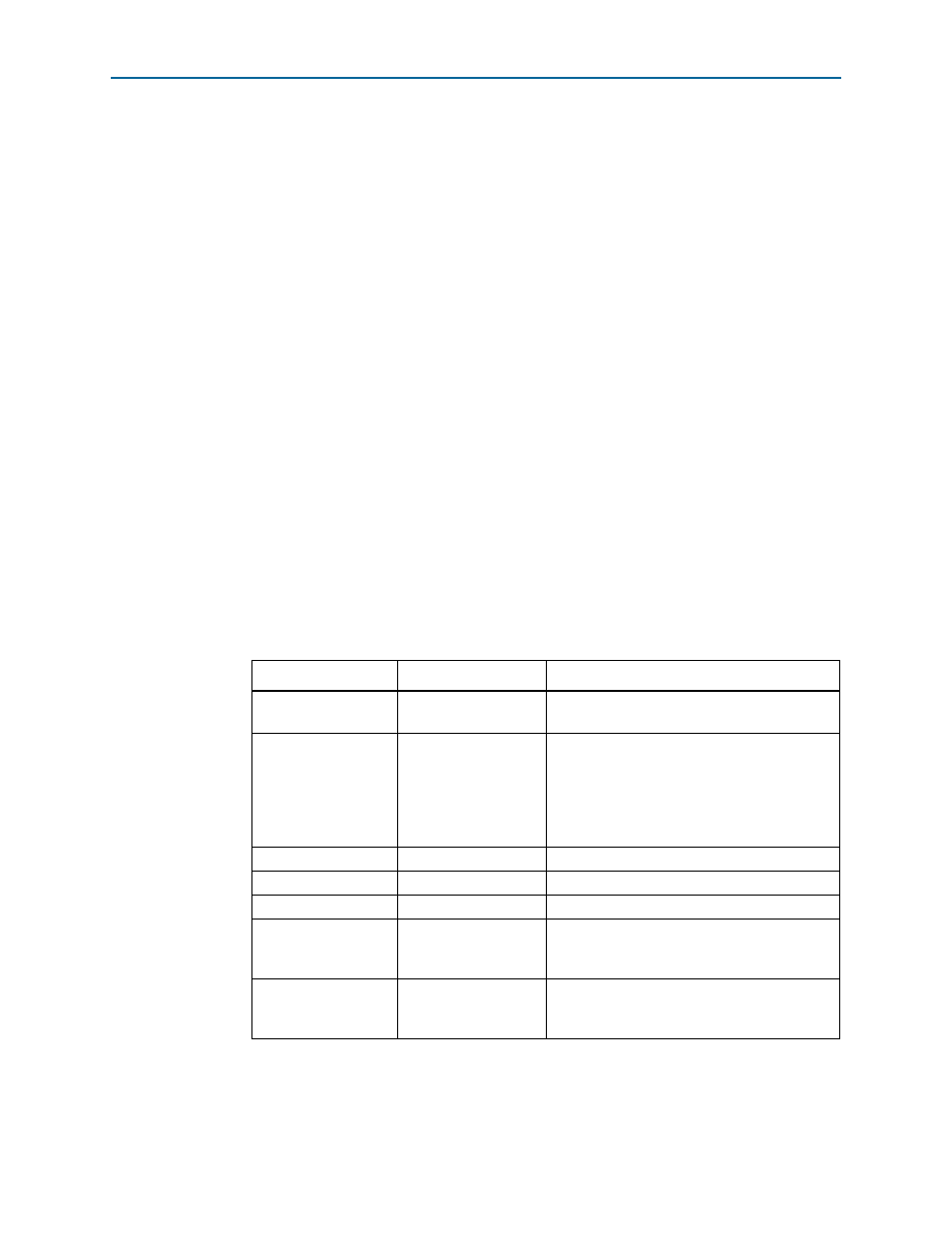

Table 4–3. Reset Signals and Corresponding Clock Domains

Reset Signal

Clock Domain

Description

reset

reconfig_clk

Resets the CPRI protocol interface. Drives the

reset controller.

gxb_powerdown

—

Powers down and resets the high-speed

transceiver block. For setup and hold times,

refer to the relevant device handbook. This

signal is not present in CPRI IP core variations

that target an Arria V, Cyclone V, or Stratix V

device.

reset_ex_delay

clk_ex_delay

Resets the extended delay measurement block.

config_reset

cpri_clkout

Resets the registers to their default values.

cpu_reset

cpu_clk

Resets the CPU interface.

mapN_rx_reset

mapN_rx_clk

Resets the MAP Channel N receiver block in

FIFO or synchronous buffer MAP

synchronization mode.

mapN_tx_reset

mapN_tx_clk

Resets the MAP Channel N transmitter block in

FIFO or synchronous buffer MAP

synchronization mode.