Altera CPRI IP Core User Manual

Page 116

6–18

Chapter 6: Signals

Clock and Reset Interface Signals

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

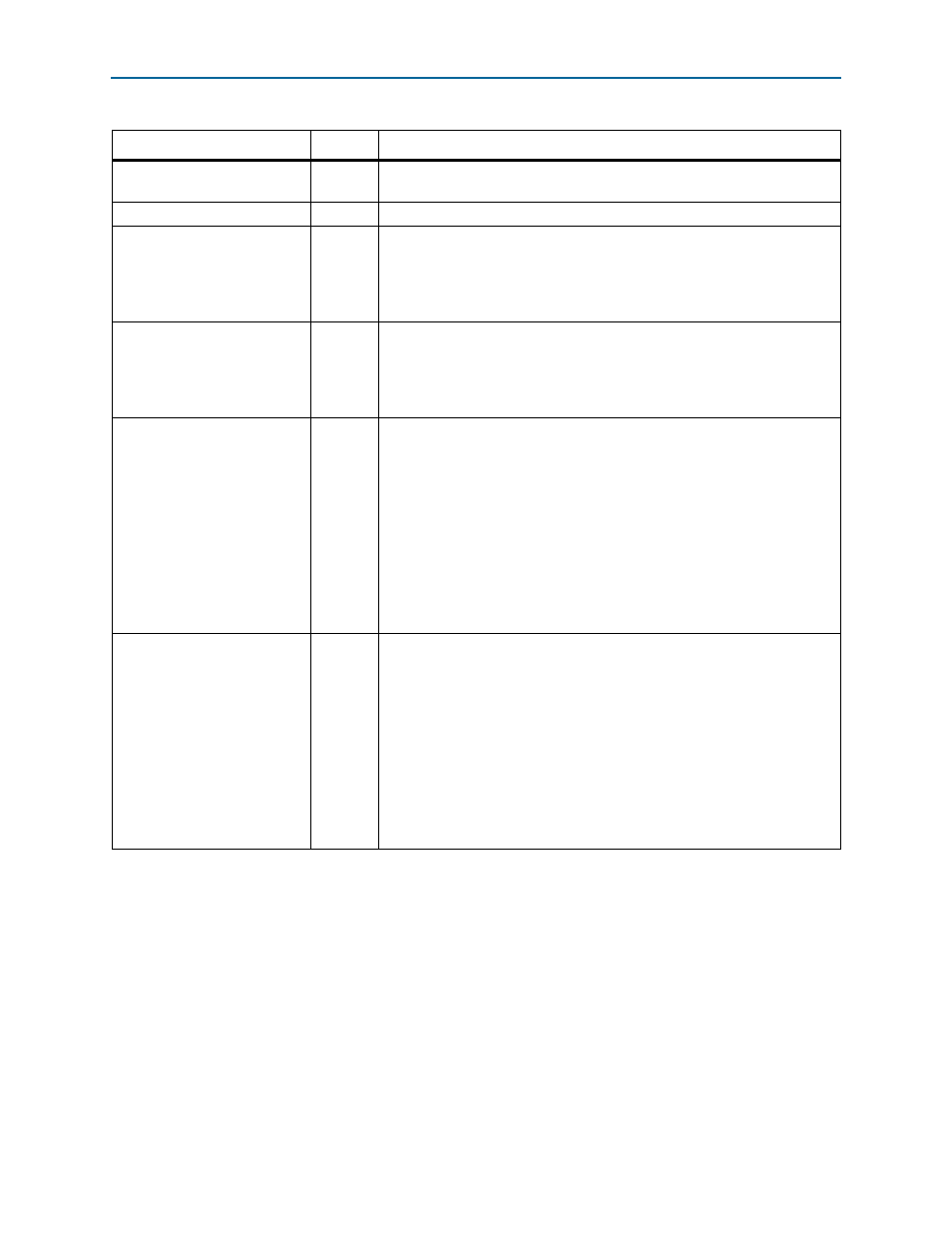

pll_clkout

Output

Generated from transceiver clock data recovery circuit. Intended to connect to

an external PLL for jitter clean-up.

cpri_clkout

Output

CPRI core clock. Provided for observation and debugging.

hw_reset_req

Output

Hardware reset request detected from received reset control word. This signal

is set after the received reset control word is set in ten consecutive basic

frames, if the

reset_out_en

bit of the

CPRI_HW_RESET

register is set. This

signal is cleared in reset. It can be used to inform the application layer of the

low-level reset request.

hw_reset_assert

Input

Indicates a reset request should be sent to the CPRI link partner on the CPRI

link, using bit 0 of the CPRI hyperframe control word Z.130.0. If the

reset_hw_en

bit of the

CPRI_HW_RESET

register is set, the CPRI IP core

sends the reset request on the CPRI link. The

hw_reset_assert

signal is

detected on the rising edge of

cpri_clkout

.

usr_pma_clk

Input

One of two extra clock signals required for CPRI IP core variations configured

at 9830.4 Mbps that target an Arria V GT device.

The CPRI IP core requires that

usr_pma_clk

be driven from a common

source with, and synchronized with, the driver of

usr_clk

. In master

clocking mode, it must have a common source with the

gxb_refclk

signal,

and in slave clocking mode, it must be driven from the cleanup PLL.

When the CPRI IP core runs at a CPRI line rate of 9830.4 Mbps, you must

drive

usr_pma_clk

at 122.88 MHz. When the IP core participates in autorate

negotiation, you must drive this clock at different frequencies for different

target CPRI line rates. Refer to

Appendix B, Implementing CPRI Link Autorate

for the required frequencies.

usr_clk

Input

One of two extra clock signals required for CPRI IP core variations configured

at 9830.4 Mbps that target an Arria V GT device.

The CPRI IP core requires that

usr_clk

be driven from a common source

with, and synchronized with, the driver of

usr_pma_clk

. it must have a

common source with the

gxb_refclk

signal, and in slave clocking mode, it

must be driven from the cleanup PLL.

When the CPRI IP core runs at a CPRI line rate of 9830.4 Mbps, you must

drive

usr_clk

at 245.76 MHz. When the IP core participates in autorate

negotiation, you must drive this clock at different frequencies for different

target CPRI line rates. Refer to

Appendix B, Implementing CPRI Link Autorate

for the required frequencies

Table 6–15. CPRI IP Core Clock and Reset Signals (Part 2 of 2)

Signal Direction

Description