Signals, Map interface signals, Map receiver signals – Altera CPRI IP Core User Manual

Page 99: Chapter 6. signals, Map interface signals –1, Map receiver signals –1, Chapter 6, signals, Chapter 6, Map receiver signals” on, Er to

December 2013

Altera Corporation

CPRI MegaCore Function

User Guide

6. Signals

This chapter describes all the top-level signals of the Altera CPRI IP core.

MAP Interface Signals

list the signals used by the MAP interface modules of the

CPRI IP core. The MAP interfaces are implemented as Avalon-ST interfaces.

f

for details about the Avalon-ST interface.

MAP Receiver Signals

The behavior of many of the MAP receiver interface signals depends on the CPRI IP

core’s current MAP Rx synchronization mode. The mode is determined by your

selection in the CPRI parameter editor and by the

CPRI_MAP_CONFIG

register

(

), as shown in

.

“MAP Receiver Interface” on page 4–18

includes a description of signal handshaking

in all three synchronization modes, and timing diagrams that illustrate the expected

behavior of these signals.For a summary of signal availability in the different

synchronization modes, refer to

.

lists the MAP receiver interface signals.

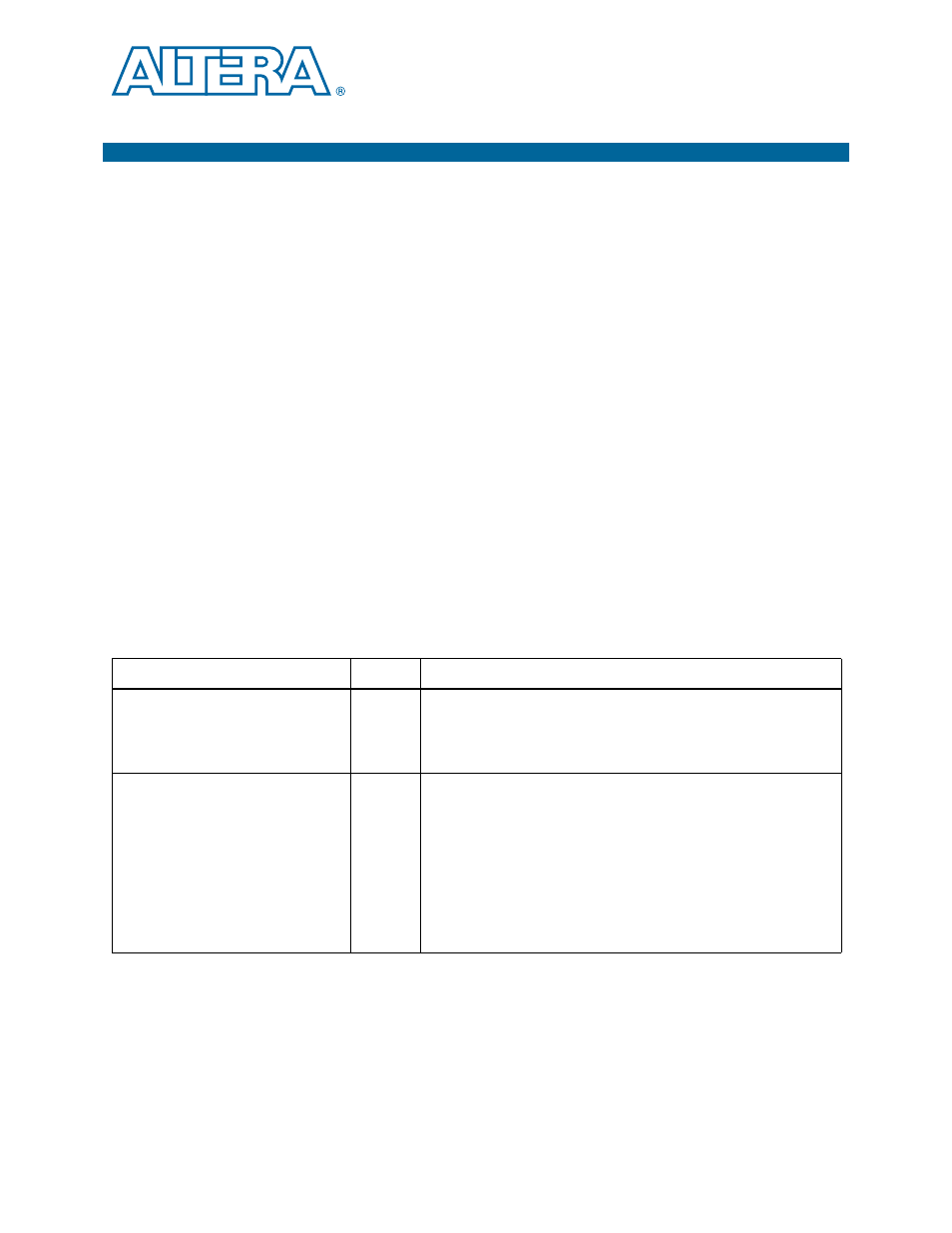

Table 6–1. MAP Receiver Interface Signals (Part 1 of 3)

Signal

Direction

Description

map{23…0}_rx_clk

Input

Clock signal for each antenna-carrier interface.

These clocks are not supported in the internally-clocked mode. In the

interally-clocked mode,

cpri_clkout

clocks the antenna-carrier

interfaces.

map{23…0}_rx_reset

Input

Reset signal for each antenna-carrier interface in synchronous buffer

mode and in FIFO mode. This reset is associated with the

mapN_rx_clk

clock.

These signals are not supported in the internally-clocked mode.

mapN_rx_reset

can be asserted asynchronously, but must stay

asserted at least one cycle of the associated clock and must be

deasserted synchronously with that clock. Refer to

for a circuit that shows how to enforce synchronous

deassertion of a reset signal.