Editor). refer to, Figure b–1, Refer to – Altera CPRI IP Core User Manual

Page 158

B–2

Appendix B: Implementing CPRI Link Autorate Negotiation

Design Implementation

CPRI MegaCore Function

December 2013

Altera Corporation

User Guide

f

For information about the Cyclone IV GX transceiver blocks and MPLLs, refer to

Cyclone IV Device Handbook. For information about the

ALTPLL_RECONFIG megafunction, refer to the

.

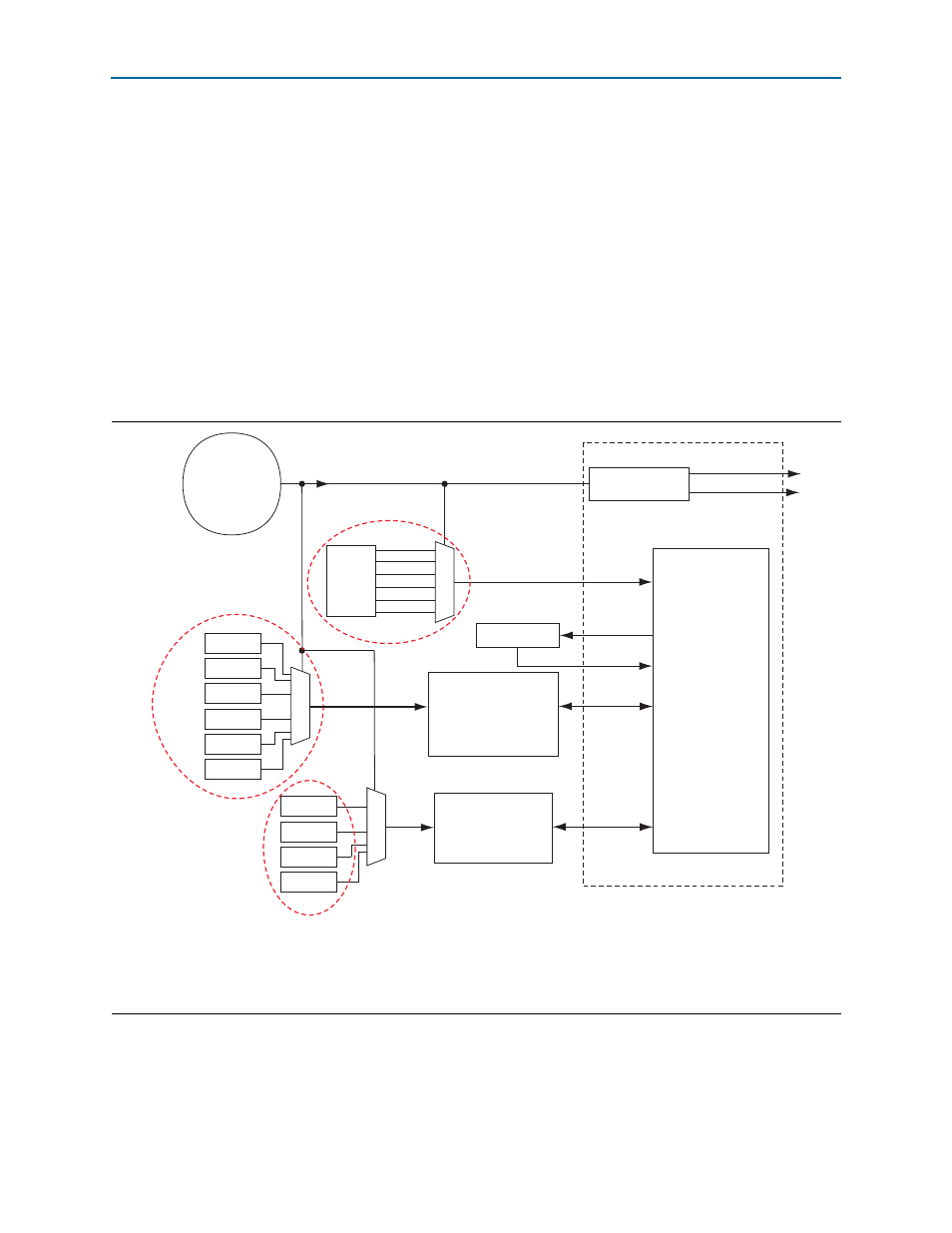

show example autorate negotiation logic block diagrams

for CPRI IP cores in slave clocking mode and master clocking mode, respectively. The

diagrams show all the potential CPRI line rates for an Arria II GX, Arria II GZ,

Arria V GX, or Stratix IV GX device. However, if you remove the options for the two

highest CPRI line rates, the examples are functional for Cyclone IV GX and

Cyclone V GX devices. If you add an option for the 9.8 Gbps CPRI line rate, the

example is functional for a Stratix V, Arria V GT, or Arria V GZ device. The examples

clarify the functionality provided by the CPRI IP core, and the logic and data you

must configure in your design outside the CPRI IP core.

Figure B–1. Autorate Negotiation in Slave Clocking Mode

Notes for

(1) Optional clock switching logic determines the value of

gxb_refclk

, depending on the desired transceiver frequency setting.

(2) You must reset the cleanup PLL configuration for different incoming and outgoing clock frequencies when the CPRI line rate changes.

(3) The number of ROMs and the rate requirements are design dependent.

CPRI MegaCore Function

gxb_refclk

AUTORATE_CONFIG

Register

ALTGX

rx_cruclk

gxb_pll_inclk

pll_inclk

pll_clkout

122.88 MHz

153.6 MHz

61.44 MHz

30.72 MHz

76.8 MHz

GPLL

Cleanup PLL

(2)

Line Rate

Software controls

line rate based on

frame synchronization

FSM feedback.

15.36 MHz

(1)

ALTGX_RECONFIG

or

Altera Transceiver

Reconfiguration Controller

(3)

ROM

3072.0 Mbps

MIF file in

ROM

4915.2 Mbps

MIF file in

ROM

6144.0 Mbps

MIF file in

ROM

2457.6 Mbps

MIF file in

ROM

1228.8 Mbps

MIF file in

ROM

614.4 Mbps

MIF file in

ALTPLL_RECONFIG

(for Cyclone IV GX

devices)

(3)

ROM

1228.8 Mbps

MIF file in

ROM

2457.6 Mbps

MIF file in

ROM

3072.0 Mbps

MIF file in

ROM

614.4 Mbps

MIF file in

datarate_en

datarate_set

To MPLL

in Cyclone IV GX

devices

reconfig_fromgxb or

reconfig_from_xcvr,

reconfig_togxb or

reconfig_to_xcvr