Altera Arria 10 Avalon-MM DMA User Manual

Page 121

Taking into account the overhead from TLP headers, this throughput is approximately 99% of the

maximum theoretical performance.

Using a 64-byte payload, the maximum theoretical throughput is far less due to the increased proportion

of the bandwidth that taken by the TLP headers. The DMA achieves the following throughput:

• 2.0 GBytes/sec back-to-back TX memory write completion

• 2.0 GBytes/sec back-to-back RX read completion throughput

• 2.0 GBytes/sec simultaneous reads and writes

Note: A 64-byte packet is worst-case packet size for Ethernet.

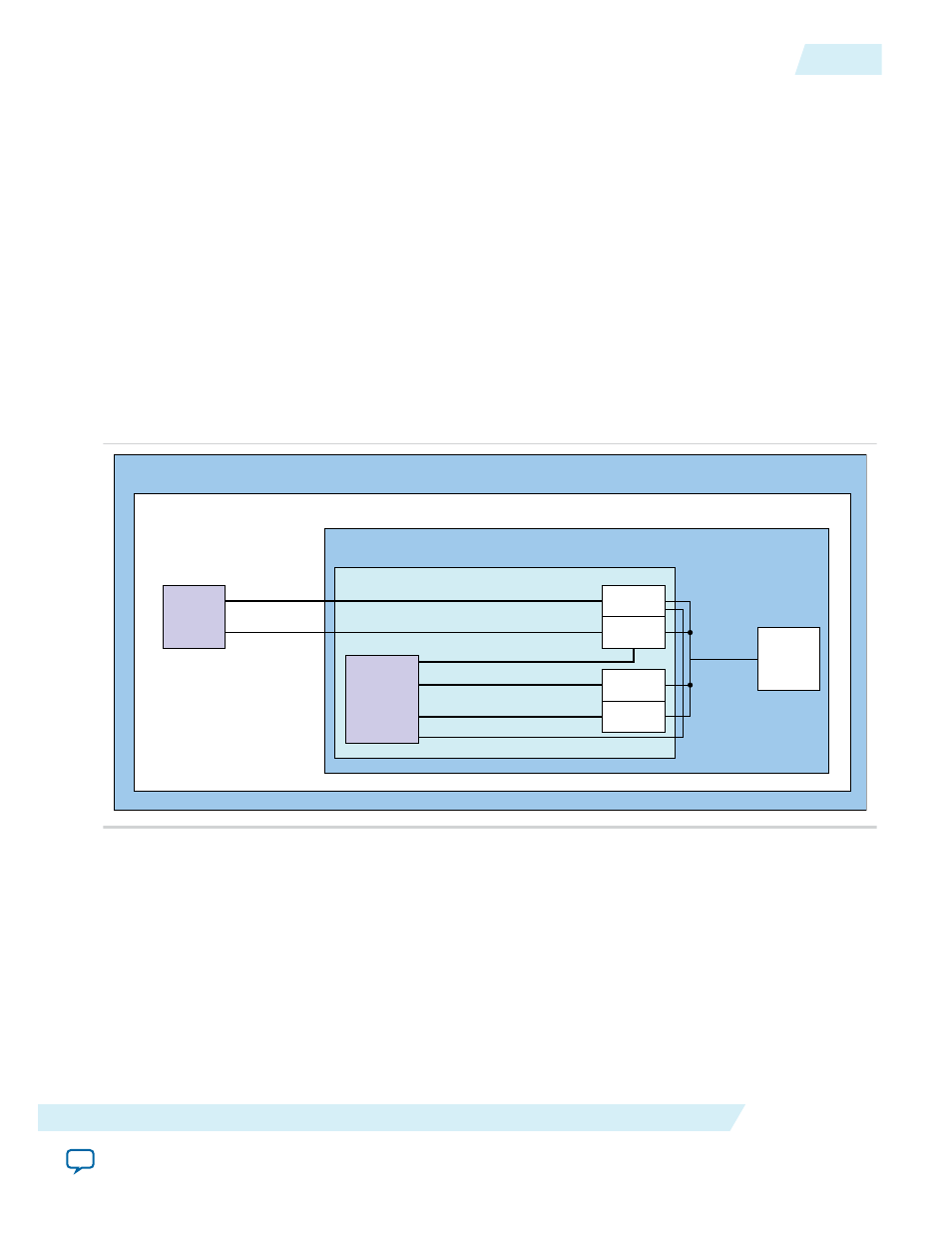

You can choose to include the DMA Descriptor Controller in the Avalon-MM bridge as shown in the

following example. Embedding the DMA Descriptor simplifies the design. Altera recommends that you

embed the DMA Descriptor Controller in the Avalon-MM bridge if you do not plan to modify it. Refer to

Getting Started with the Arria 10 Avalon-MM DMA for an example that includes the embedded DMA

Descriptor Controller.

Figure 9-4: Avalon-MM DMA Block Diagram with Embedded DMA Descriptor Controller

PCIe Avalon-MM Bridge

Hard IP for PCIe Using Avalon-MM Interface

Altera FPGA

Qsys System

with Internal Descriptor Controller

Memory

Read DMA

Write DMA

Hard IP

for PCIe

RX Master

TX Slave

DMA

Descriptor

Controller

Avalon-MM Burst

Master 256 Bits

Avalon-MM Burst

Master 256 Bits

Avalon-MM Master

Avalon-MM Slave Single DWORD

Avalon-ST Control/Status

Avalon-ST

256 Bits

FIFO

Internal Conduit

UG-01145_avmm_dma

2015.05.14

Arria 10 Avalon-MM DMA for PCI Express

9-9

IP Core Architecture

Altera Corporation