Features, Features -2 – Altera Arria 10 Avalon-MM DMA User Manual

Page 6

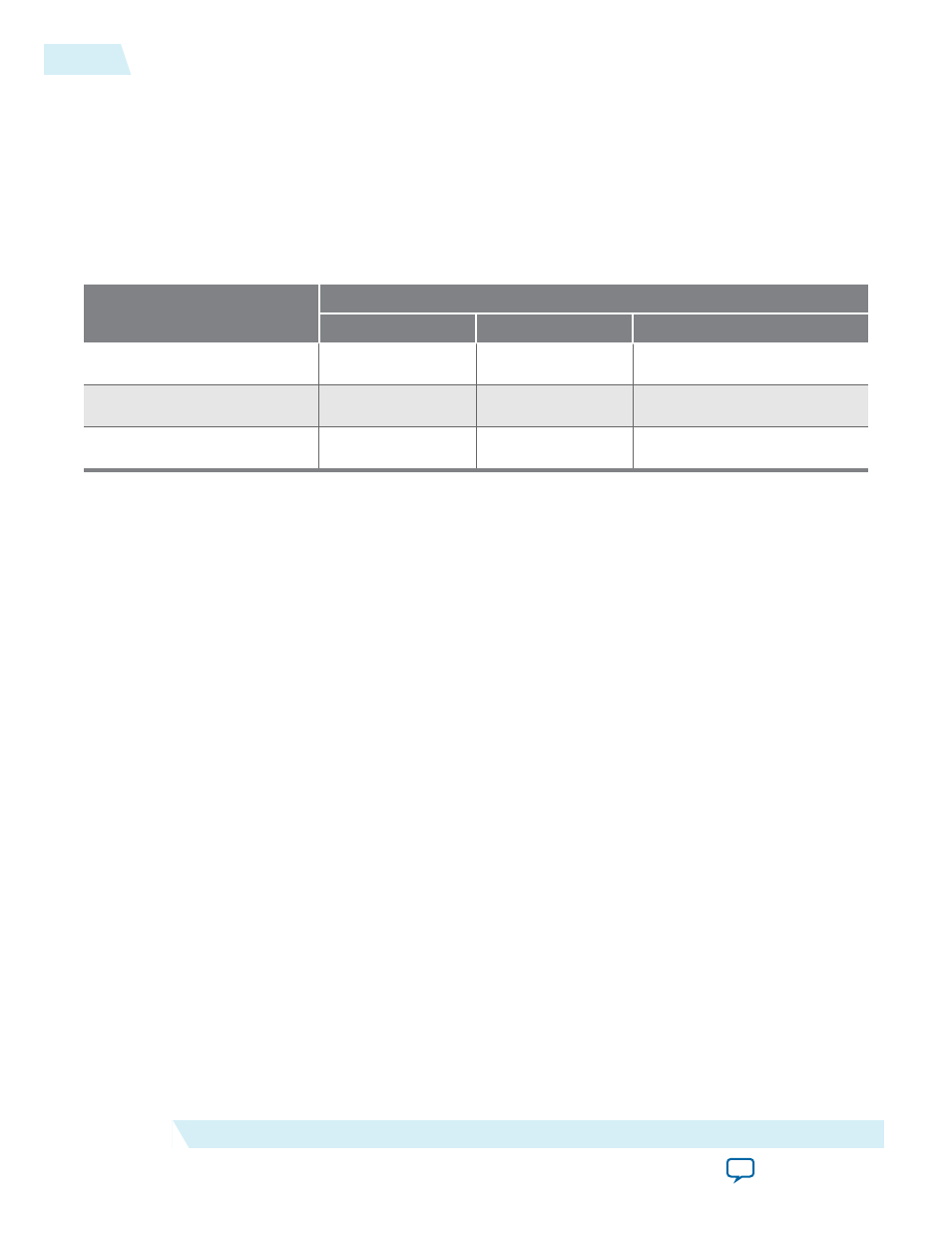

Table 1-1: PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen1, Gen2, and Gen3 for 2, 4, and 8

lanes. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per second for Gen2, and

8.0 giga-transfers per second for Gen3. This table provides bandwidths for a single transmit (TX) or receive (RX)

channel. The numbers double for duplex operation. Gen1 and Gen2 use 8B/10B encoding which introduces a 20%

overhead. In contrast, Gen3 uses 128b/130b encoding which reduces the data throughput lost to encoding to less

than 1%.

Units are Gigabits per second (Gbps).

Link Width

×2

×4

×8

PCI Express Gen1 (2.5 Gbps)

N/A

N/A

16 Gbps

PCI Express Gen2 (5.0 Gbps)

N/A

16 Gbps

32 Gbps

PCI Express Gen3 (8.0 Gbps)

15.75 Gbps

31.51 Gbps

63Gbps

Related Information

•

•

•

Features

New features in the Quartus

®

II 15.0 software release:

• Added Enable Altera Debug Master Endpoint (ADME) parameter to support optional Native PHY

register programming with the Altera System Console.

• Added support for downstream burst read with a payload of size up to 4 KBytes, if Enable burst

capability for RXM BAR2 port is turned on in the Parameter Editor. Previous maximum downstream

read request payload size was 512 bytes.

The Arria 10 Avalon-MM DMA for PCI Express supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

hard IP.

• Native support for Gen1 x8, Gen2 x4, Gen2 x8, Gen3 x4, Gen3 x8 for Endpoints. The variant

downtrains when plugged into a lesser link width or changes to a different maximum link rate.

• Dedicated 16 KByte receive buffer.

• Support for 128- or 256-bit Avalon-MM interface to Application Layer with embedded DMA up to

Gen3 ×8 data rate.

• Support for 32- or 64-bit addressing for the Avalon-MM interface to the Application Layer.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

1-2

Features

UG-01145_avmm_dma

2015.05.14

Altera Corporation

Datasheet