Power management, Power management -12 – Altera Arria 10 Avalon-MM DMA User Manual

Page 32

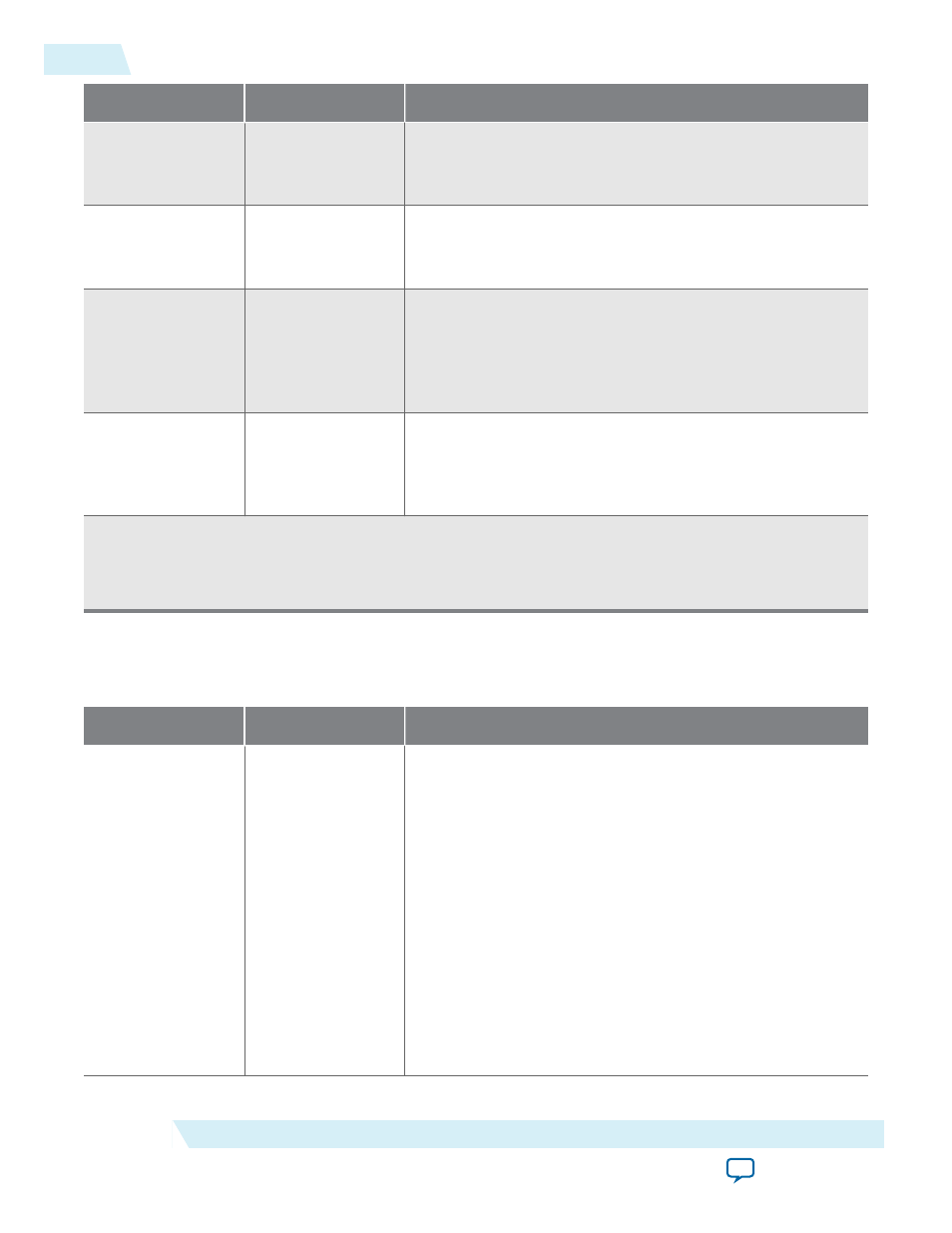

Parameter

Value

Description

Table Offset

[31:0]

Points to the base of the MSI-X Table. The lower 3 bits of the

table BAR indicator (BIR) are set to zero by software to form a

32-bit qword-aligned offset

(1)

. This field is read-only.

Table BAR

Indicator

[2:0]

Specifies which one of a function’s BARs, located beginning at

0x10 in Configuration Space, is used to map the MSI-X table

into memory space. This field is read-only. Legal range is 0–5.

Pending Bit

Array (PBA)

Offset

[31:0]

Used as an offset from the address contained in one of the

function’s Base Address registers to point to the base of the

MSI-X PBA. The lower 3 bits of the PBA BIR are set to zero by

software to form a 32-bit qword-aligned offset. This field is

read-only.

Pending BAR

Indicator

[2:0]

Specifies the function Base Address registers, located

beginning at 0x10 in Configuration Space, that maps the MSI-

X PBA into memory space. This field is read-only. Legal range

is 0–5.

Note:

1. Throughout this user guide, the terms word, dword and qword have the same meaning that they have

in the PCI Express Base Specification. A word is 16 bits, a dword is 32 bits, and a qword is 64 bits.

Power Management

Table 3-9: Power Management Parameters

Parameter

Value

Description

Endpoint L0s

acceptable

latency

Maximum of 64 ns

Maximum of 128 ns

Maximum of 256 ns

Maximum of 512 ns

Maximum of 1 us

Maximum of 2 us

Maximum of 4 us

No limit

This design parameter specifies the maximum acceptable

latency that the device can tolerate to exit the L0s state for any

links between the device and the root complex. It sets the

read-only value of the Endpoint L0s acceptable latency field of

the

Device Capabilities Register

(0x084).

This Endpoint does not support the L0s or L1 states. However,

in a switched system there may be links connected to switches

that have L0s and L1 enabled. This parameter is set to allow

system configuration software to read the acceptable latencies

for all devices in the system and the exit latencies for each link

to determine which links can enable Active State Power

Management (ASPM). This setting is disabled for Root Ports.

The default value of this parameter is 64 ns. This is the safest

setting for most designs.

3-12

Power Management

UG-01145_avmm_dma

2015.05.14

Altera Corporation

Parameter Settings