Generating the testbench, Generating the testbench -2 – Altera Arria 10 Avalon-MM DMA User Manual

Page 15

plan to replace the Descriptor Controller IP core with your own implementation, do not turn on the

Instantiate internal descriptor controller in the parameter editor when parameterizing the IP core.

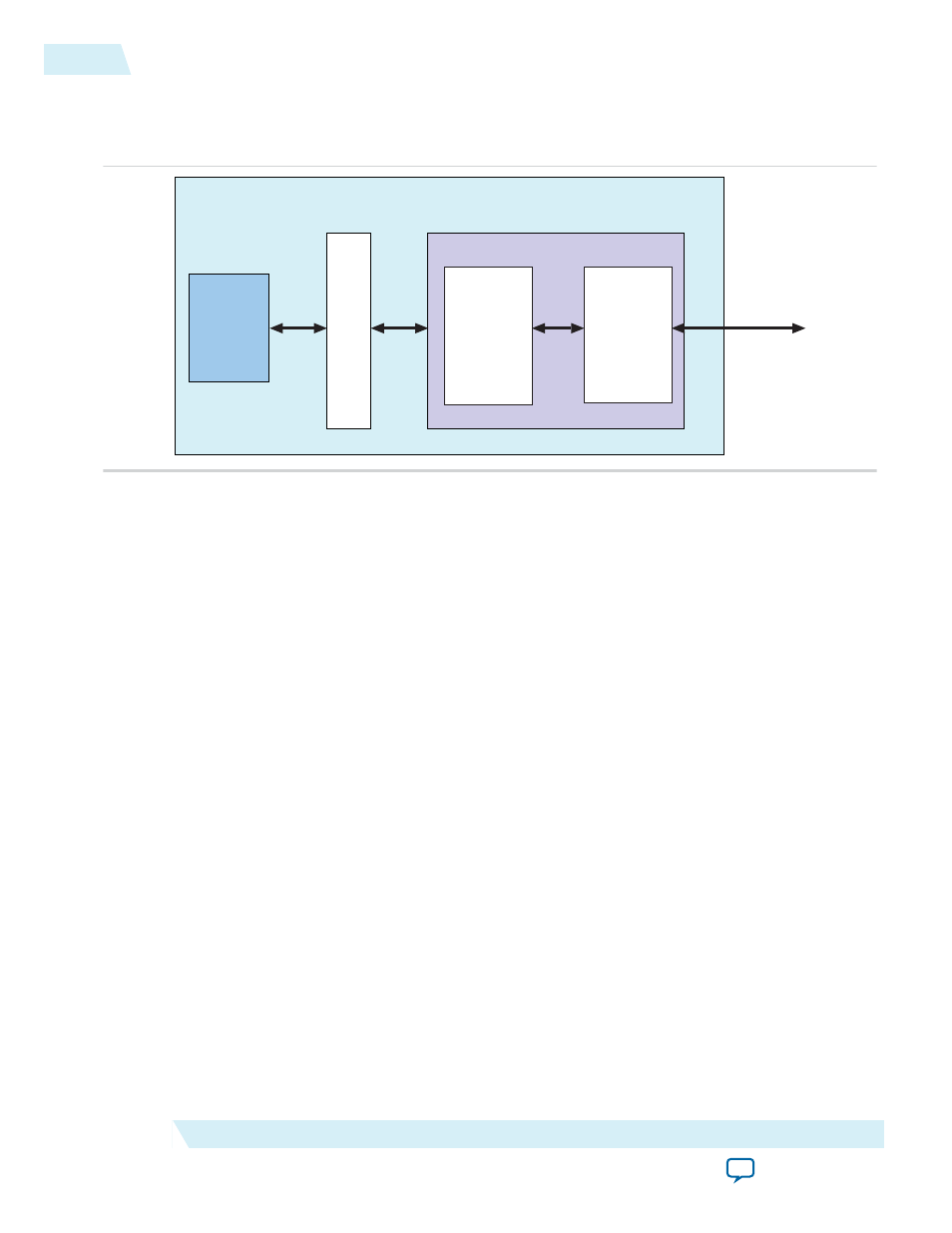

Figure 2-1: Block Diagram of Arria 10 Avalon-MM DMA for PCI Express

Transaction,

Hard IP for PCIe

Data Link,

and

Physical

Layers

On-Chip

Memory

DMA Data

Qsys System Design Arria 10 Hard IP for PCI Express

PCI Express

Link

Gen3 x8

Descriptor

Controller

DMA Engine

Avalon-MM to

PCIe TLP

Bridge

Arria 10 Hard IP for PCI Express Using Avalon-MM

Inteface and DMA

In

ter

connec

t

Related Information

•

Arria 10 Avalon-MM DMA for PCI Express

on page 9-8

•

DMA Descriptor Controller Registers

on page 6-15

Generating the Testbench

1. Copy the example design,

ep_g3x8_avmm256_integrated.qsys

, from the installation directory:

<install_dir>/ip/altera/altera_pcie/altera_pcie_a10_ed/example_design/a10/

to your working directory.

2. Start Qsys, by typing the following command:

qsys-edit

3. Open

ep_g3x8_avmm256_integrated.qsys

.

2-2

Generating the Testbench

UG-01145_avmm_dma

2015.05.14

Altera Corporation

Getting Started with the Avalon-MM DMA