Altera Arria 10 Avalon-MM DMA User Manual

Page 72

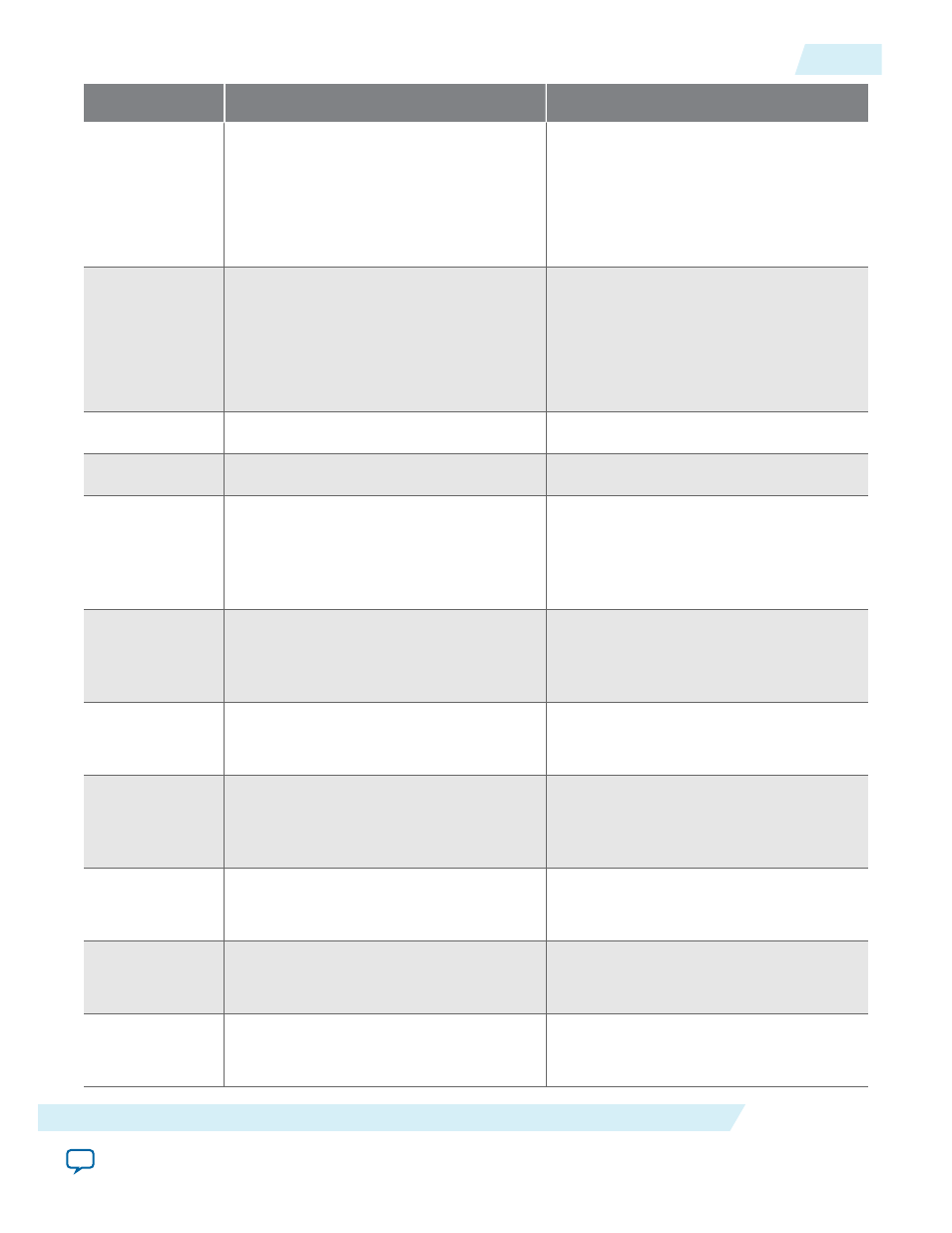

Byte Address

Hard IP Configuration Space Register

Corresponding Section in PCIe Specification

0x008

Class Code, Revision ID

Type 0 Configuration Space Header

Type 1 Configuration Space Header

The Type 1 Configuration Space is not

available for the Avalon-MM with DMA

interface

0x00C

BIST, Header Type, Primary Latency Timer,

Cache Line Size

Type 0 Configuration Space Header

Type 1 Configuration Space Header

The Type 1 Configuration Space is not

available for the Avalon-MM with DMA

interface

0x010

Base Address 0

Base Address Registers

0x014

Base Address 1

Base Address Registers

0x018

Base Address 2

Secondary Latency Timer, Subordinate Bus

Number, Secondary Bus Number, Primary

Bus Number

Base Address Registers

Secondary Latency Timer, Type 1

Configuration Space Header, Primary

Bus Number

0x01C

Base Address 3

Secondary Status, I/O Limit, I/O Base

Base Address Registers

Secondary Status Register ,Type 1

Configuration Space Header

0x020

Base Address 4

Memory Limit, Memory Base

Base Address Registers

Type 1 Configuration Space Header

0x024

Base Address 5

Prefetchable Memory Limit, Prefetchable

Memory Base

Base Address Registers

Prefetchable Memory Limit, Prefetchable

Memory Base

0x028

Reserved

Prefetchable Base Upper 32 Bits

N/A

Type 1 Configuration Space Header

0x02C

Subsystem ID, Subsystem Vendor ID

Prefetchable Limit Upper 32 Bits

Type 0 Configuration Space Header

Type 1 Configuration Space Header

0x030

I/O Limit Upper 16 Bits, I/O Base Upper 16

Bits

Type 0 Configuration Space Header

Type 1 Configuration Space Header

UG-01145_avmm_dma

2015.05.14

Correspondence between Configuration Space Registers and the PCIe...

6-3

Registers

Altera Corporation