Altera Arria 10 Avalon-MM DMA User Manual

Page 47

If burst mode is not enabled, the RX Master module only supports 32-bit read or write request. All other

requests received from the PCIe link are considered a violation of this device’s programming model, and

are therefore handled with the PCIe Completer Abort status. You can enable burst mode for BAR2 using

32-bit addressing or BAR2 and BAR3 using 64-bit addressing. When enabled, the module supports

dword, burst read or write requests. When the Descriptor Controller is internally instantiated, the RX

Master for BAR0 is used internally and not available for other uses.

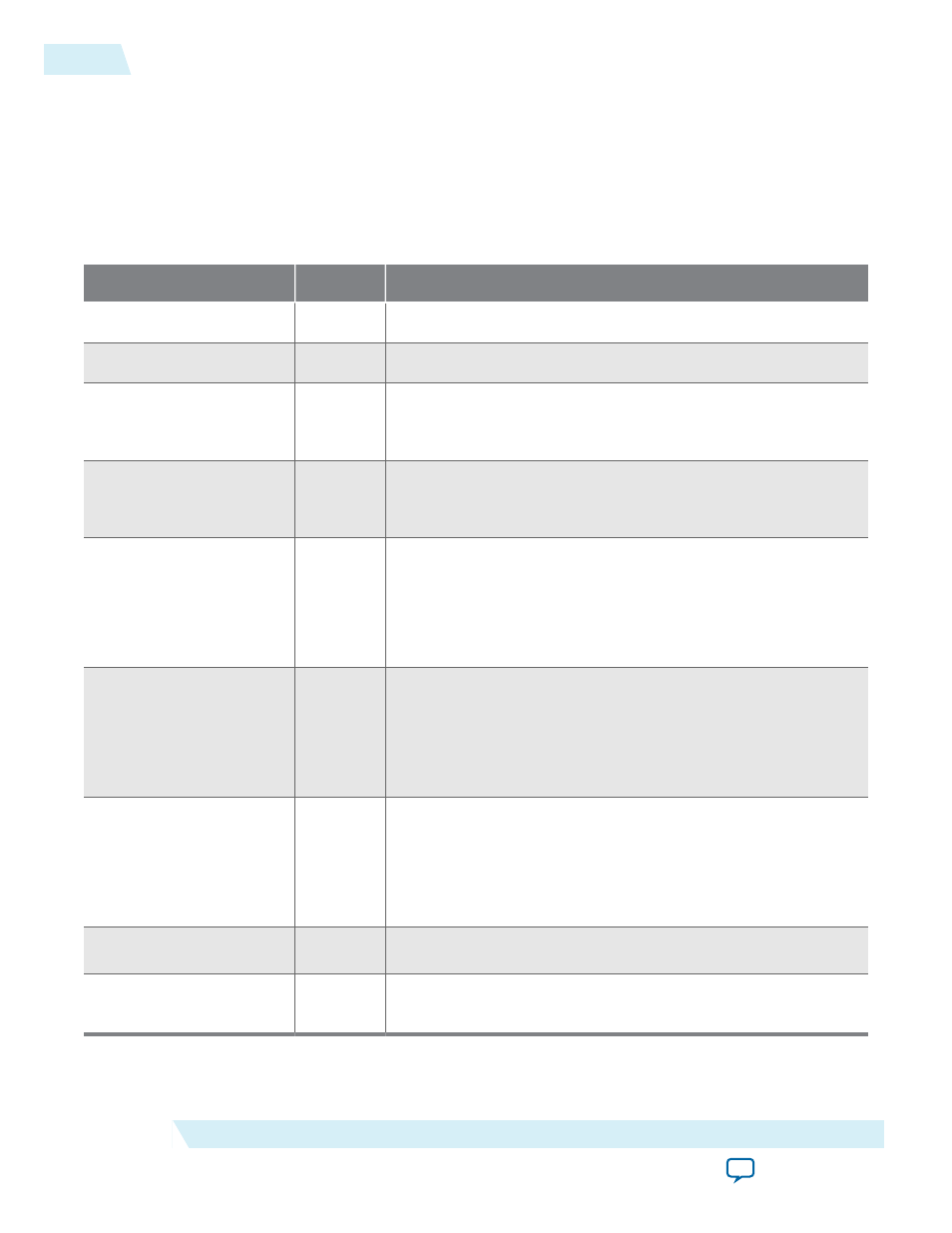

Table 5-3: RX Master Control Interface Ports for BAR Access

Each BAR has one corresponding RX Master Control interface. In this table, <n> is the BAR number.

Signal Name

Direction

Description

RxmRead_<n>_o

Output

When asserted, indicates an Avalon-MM read request.

RxmWrite_<n>_o

Output

When asserted, indicates an Avalon-MM write request.

RxmAddress_<n>_o[<w>-

1:0]

Output

Specifies the Avalon-MM byte address. Because all addresses are

byte addresses, the meaningful bits of this address are [<w>-1:2].

Bits 1 and 0 have a value of 0. <w> can be 32 or 64.

RxmBurstCount_<n>_

o[5:0]

Output

Specifies the burst count in dwords (32 bits). This optional signal

is available for BAR2 when you turn on Enable burst capabili‐

ties for RXM BAR2 ports.

RxmByteEnable_<n>_

o[<w>:0]

Output

Specifies the valid bytes of data to be written. <w> has the

following values:

• 4: for the non-bursting RX Master

• 32: for the bursting 128-bit Avalon-MM interface

• 64: for the bursting 256-bit Avalon-MM interface

RxmDataWrite_<n>_

o[<w>:0]

Output

Specifies the Avalon-MM write data. <w> has the following

values:

• 32: for the non-bursting RX Master

• 128: for the bursting 128-bit Avalon-MM interface

• 256: for the bursting 256-bit Avalon-MM interface

RxmReadData_<n>_i[<w>

:0]

Input

Specifies the Avalon-MM read data. <w> has the following

values:

• 32: for the non-bursting RX Master

• 128: for the bursting 128-bit Avalon-MM interface

• 256: for the bursting 256-bit Avalon-MM interface

RxmReadDataValid_<n>_

i[31:0]

Input

When asserted, indicates that RxmReadData_i[31:0]is

valid.

RxmWaitRequest_<n>_i

Input

When asserted indicates that the control register access Avalon-

MM slave port is not ready to respond.

5-6

RX Master Module

UG-01145_avmm_dma

2015.05.14

Altera Corporation

IP Core Interfaces