Tx slave module, Tx slave module -7 – Altera Arria 10 Avalon-MM DMA User Manual

Page 48

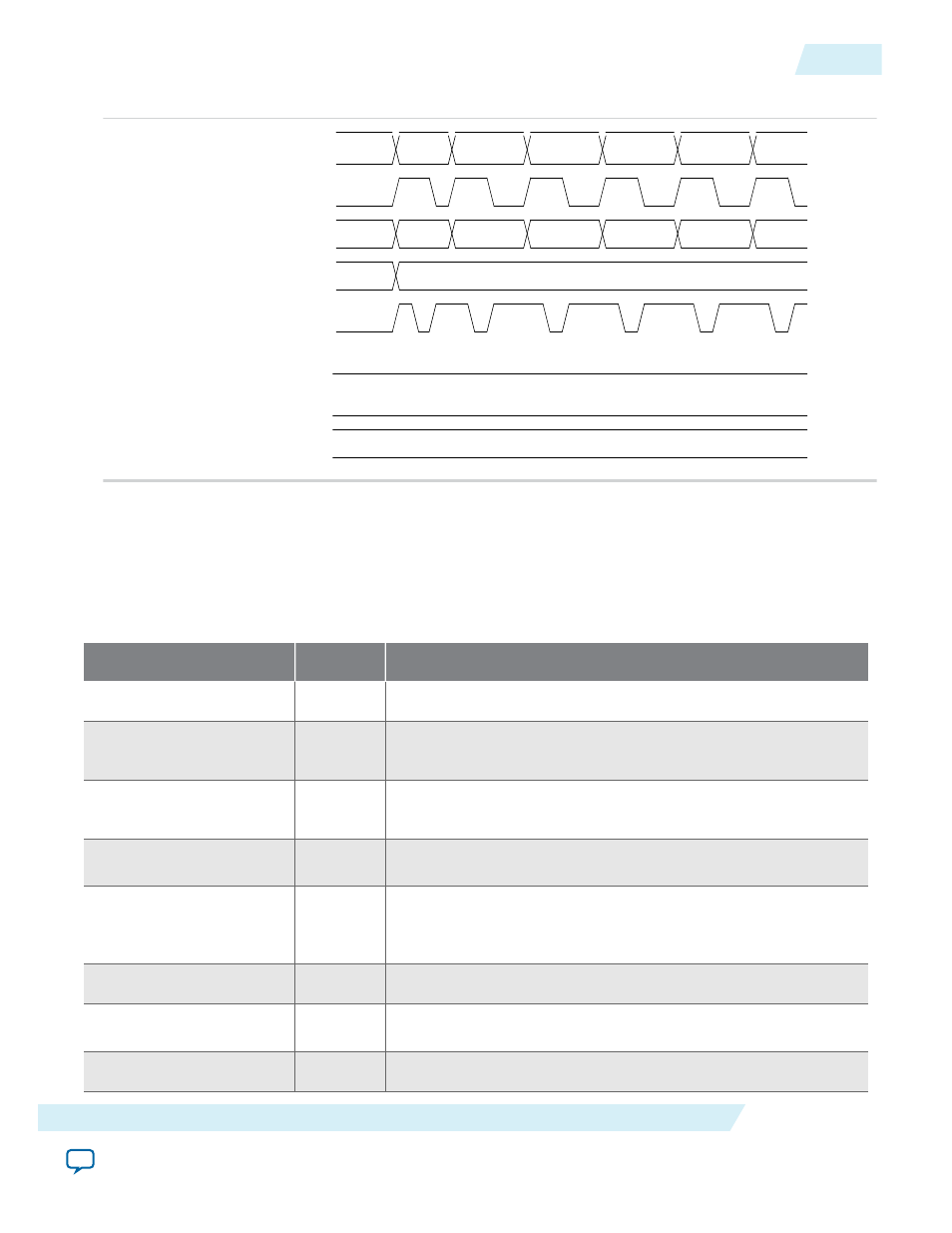

Figure 5-5: RXM Master Writes To Memory in the Avalon-MM Address Space

AvRxmAddress_<n>_o[63:0]

AvRxmWrite_<n>_o

AvRxmWriteData_<n>_o[31:0]

AvRxmByteEnable_<n>_o[3:0]

AvRxmWaitRequest_<n>_i

AvRxmRead_<n>_o

AvRxmReadDataValid_<n>_i

AvRxmReadData_<n>_i[31:0]

800041080

00001010

00000000

00000001

00003800

00000000

8000410C

80004110

80004114

80004118

80004100

128: for the bursting 128-bit Avalon-MM interface

TX Slave Module

The TX Slave module translates Avalon-MM master read and write requests to PCI Express TLPs for the

Root Port. The TX Slave Control module supports a single outstanding non-bursting request. It typically

sends status updates to the host. This is a 32-bit Avalon-MM slave bus.

Table 5-4: TX Slave Control

Signal Name

Direction

Description

TxsChipSelect_i

Input

When asserted, indicates that this slave interface is selected.

TxsRead_i

Input

When asserted, specifies an TX Avalon-MM slave read request

from the Root Complex or Root Port.

TxsWrite_i

Input

When asserted, specifies an TX Avalon-MM slave write request

to the Root Complex or Root Port.

TxsWriteData_i[<w>-

1:0]

Input

Specifies the Avalon-MM data for a write command.

TxsAddress_i[<w>-1:0]

Input

Specifies the Avalon-MM byte address for the read or write

command. The width of this address bus is specified by the

parameter Address width of accessible PCIe memory space.

TxsByteEnable_i[3:0]

Input

Specifies the valid bytes for a write command.

TxsReadData_o[<w>-

1:0]

Output

Specifies the read completion data.

TxsReadDataValid_o

Output

When asserted, indicates that

TxsReadData_o[31:0]

is valid.

UG-01145_avmm_dma

2015.05.14

TX Slave Module

5-7

IP Core Interfaces

Altera Corporation