Altera Arria 10 Avalon-MM DMA User Manual

Page 88

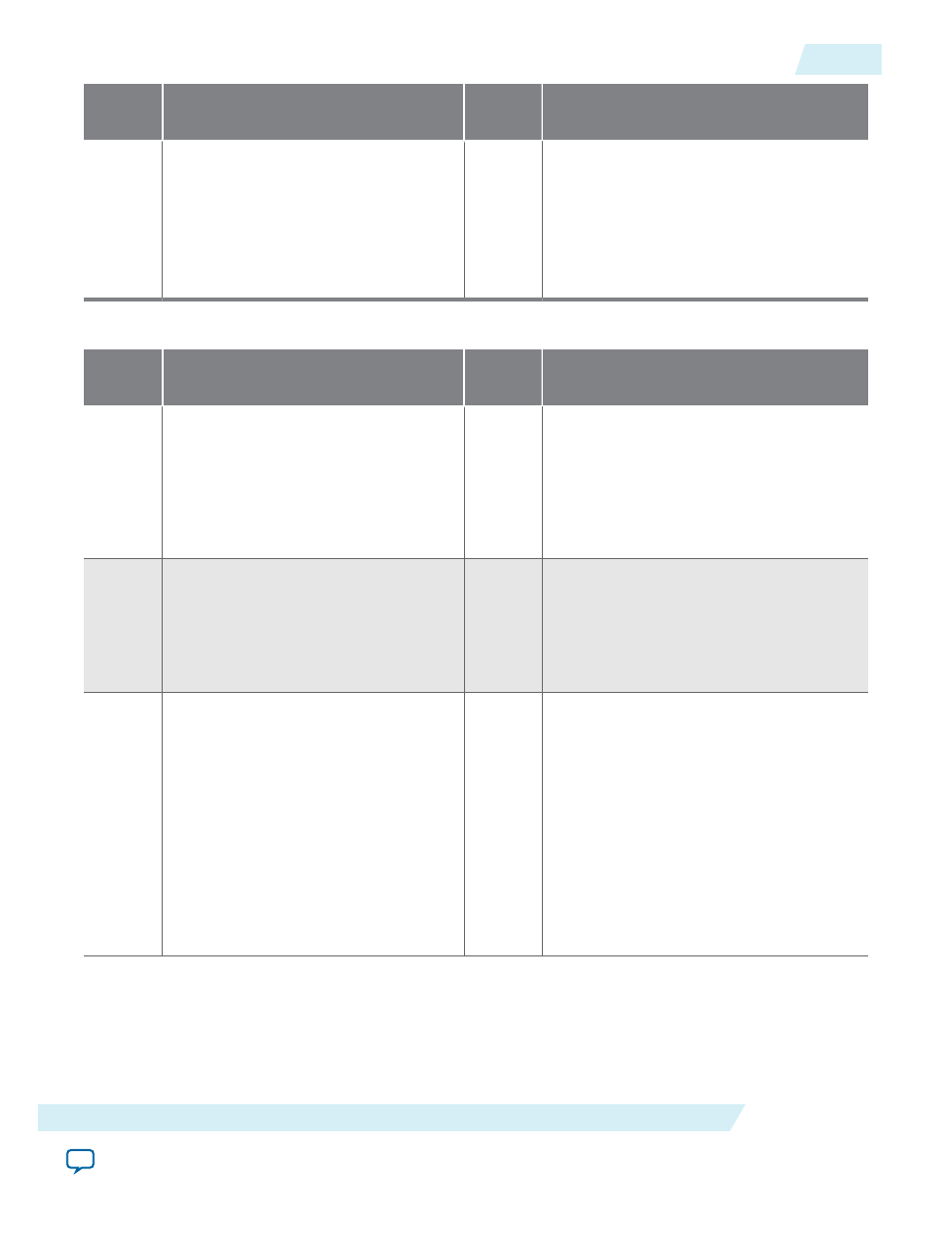

Address

Offset

Register

Access

Description

0x001

8

RD_CONTROL

RW

[31:1] Reserved.

[0]

Done

. When set, the Descriptor

Controller writes the

Done

bit for each

descriptor in the status table. The

Descriptor Controller sends a single MSI

interrupt after the final descriptor

completes.

Table 6-16: DMA Descriptor Controller Registers for Write DMAs

Address

Offset

Register

Access

Description

0x010

0

RC Write Status and Descriptor

Base (Low)

R/W

Specifies the lower 32-bits of the base

address of the write status and descriptor

table in the Root Complex memory. This

address must be on a 32-byte boundary.

Software must program this register after

programming the upper 32-bit register at

offset 0x104.

0x010

4

RC Write Status and Descriptor

Base (High)

R/W

Specifies the upper 32-bits of the base

address of the write status and descriptor

table in the Root Complex memory.

Software must program this register

before programming the lower 32-bit

register at offset 0x100.

0x010

8

EP Write Status and Descriptor

FIFO Base (Low)

RW

Specifies the lower 32 bits of the base

address of the write descriptor table in

Endpoint memory. The Write Descriptor

Controller requests descriptors from Root

Complex memory and writes the descrip‐

tors to this location. The address is the

Avalon-MM address of the Descriptor

Controller's Write Descriptor Table

Avalon-MM Slave Port as seen by the

Read DMA Avalon-MM Master Port.

Software must program this register after

programming the upper 32-bit register at

offset 0x10C.

UG-01145_avmm_dma

2015.05.14

DMA Descriptor Controller Registers

6-19

Registers

Altera Corporation