Msi interrupts for endpoints, Msi interrupts for endpoints -19 – Altera Arria 10 Avalon-MM DMA User Manual

Page 60

Signal

Direction

Description

Note that not all simulation models assert the Transaction Layer

error bit in conjunction with the Data Link Layer error bit.

Related Information

•

Reset and Clocks

•

on page 7-4

•

•

MSI Interrupts for Endpoints

The MSI interrupt notifies the host when a DMA operation has completed. After the host receives this

interrupt, it can poll the DMA read or write status table to determine which entry or entries have the

done

bit set. This mechanism allows host software to avoid continuous polling of the status table

done

bits.

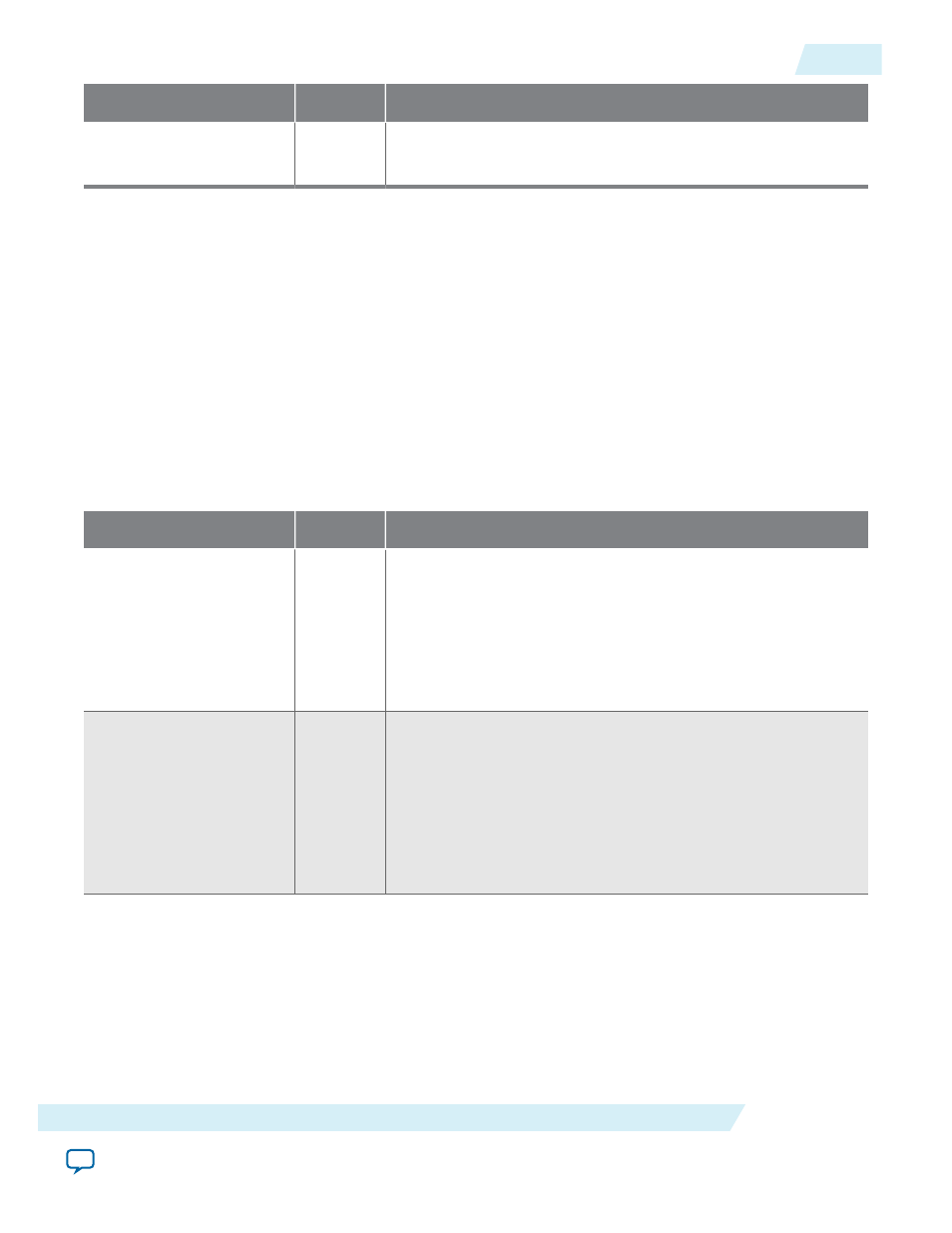

Table 5-19: MSI Interrupt

Signal

Direction

Description

MSIIntfc_o[81:0]

Output

This bus provides the following MSI address, data, and enabled

signals:

•

MSIIntfc_o[81]

: Master enable

•

MSIIntfc_o[80

}: MSI enable

•

MSIIntfc_o[79:64]

: MSI data

•

MSIIntfc_o[63:0]

: MSI address

MSIXIntfc_o[15:0]

Output

Provides for system software control of MSI-X as defined in

Section 6.8.2.3 Message Control for MSI-X in the PCI Local Bus

Specification, Rev. 3.0. The following fields are defined:

•

MSIXIntfc_o[15]

: Enable

•

MSIXIntfc_o[14]

: Mask

•

MSIXIntfc_o[13:11]

: Reserved

•

MSIXIntfc_o[10:0]

: Table size

UG-01145_avmm_dma

2015.05.14

MSI Interrupts for Endpoints

5-19

IP Core Interfaces

Altera Corporation