Altera Arria 10 Avalon-MM DMA User Manual

Page 96

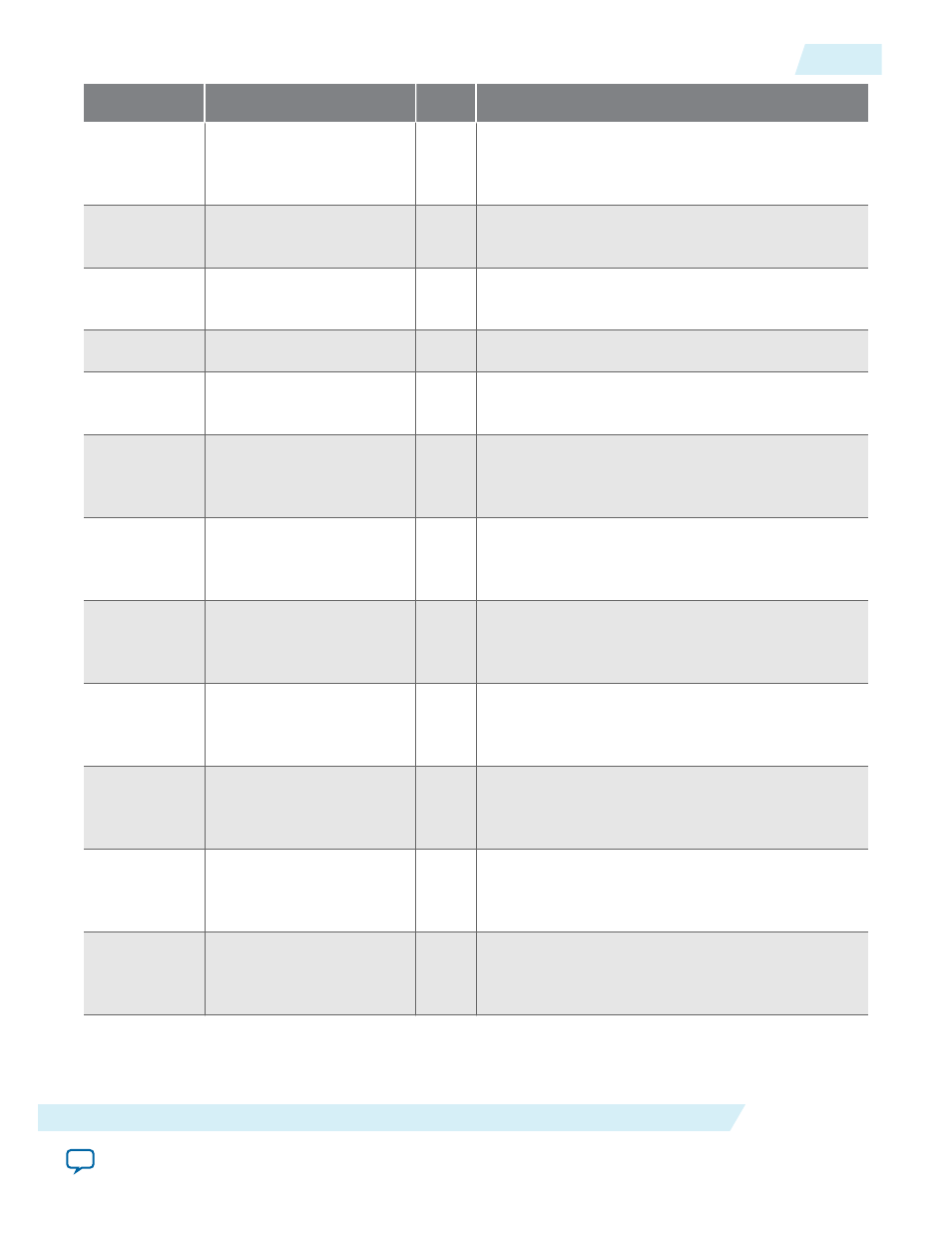

Byte Offset

Register

Dir

Description

14'h0018

cfg_sec_ctrl[15:0]

O

Secondary bus Control and Status register of the

PCI-Express capability. This register is only

available in Root Port mode.

14'h001C

cfg_secbus[7:0]

O

Secondary bus number. Available in Root Port

mode.

14'h0020

cfg_subbus[7:0]

O

Subordinate bus number. Available in Root Port

mode.

14'h0024

cfg_msi_addr_low[31:0]

O

cfg_msi_add[31:0]

is the MSI message address.

14'h0028

cfg_msi_addr_hi[63:32]

O

cfg_msi_add[63:32]

is the MSI upper message

address.

14'h002C

cfg_io_bas[19:0]

O

The IO base register of the Type1 Configuration

Space. This register is only available in Root Port

mode.

14'h0030

cfg_io_lim[19:0]

O

The IO limit register of the Type1 Configuration

Space. This register is only available in Root Port

mode.

14'h0034

cfg_np_bas[11:0]

O

The non-prefetchable memory base register of the

Type1 Configuration Space. This register is only

available in Root Port mode.

14'h0038

cfg_np_lim[11:0]

O

The non-prefetchable memory limit register of the

Type1 Configuration Space. This register is only

available in Root Port mode.

14'h003C

cfg_pr_bas_low[31:0]

O

The lower 32 bits of the prefetchable base register of

the Type1 Configuration Space. This register is only

available in Root Port mode.

14'h0040

cfg_pr_bas_hi[43:32]

O

The upper 12 bits of the prefetchable base registers

of the Type1 Configuration Space. This register is

only available in Root Port mode.

14'h0044

cfg_pr_lim_low[31:0]

O

The lower 32 bits of the prefetchable limit registers

of the Type1 Configuration Space. This register is

only available in Root Port mode.

UG-01145_avmm_dma

2015.05.14

Control Register Access (CRA) Avalon-MM Slave Port

6-27

Registers

Altera Corporation