Read descriptor controller avalon-mm master port – Altera Arria 10 Avalon-MM DMA User Manual

Page 52

Bits

Name

Description

[153:14

6]

DMA Descriptor ID

Specifies up to 128 descriptors.

[159:15

4]

Reserved

—

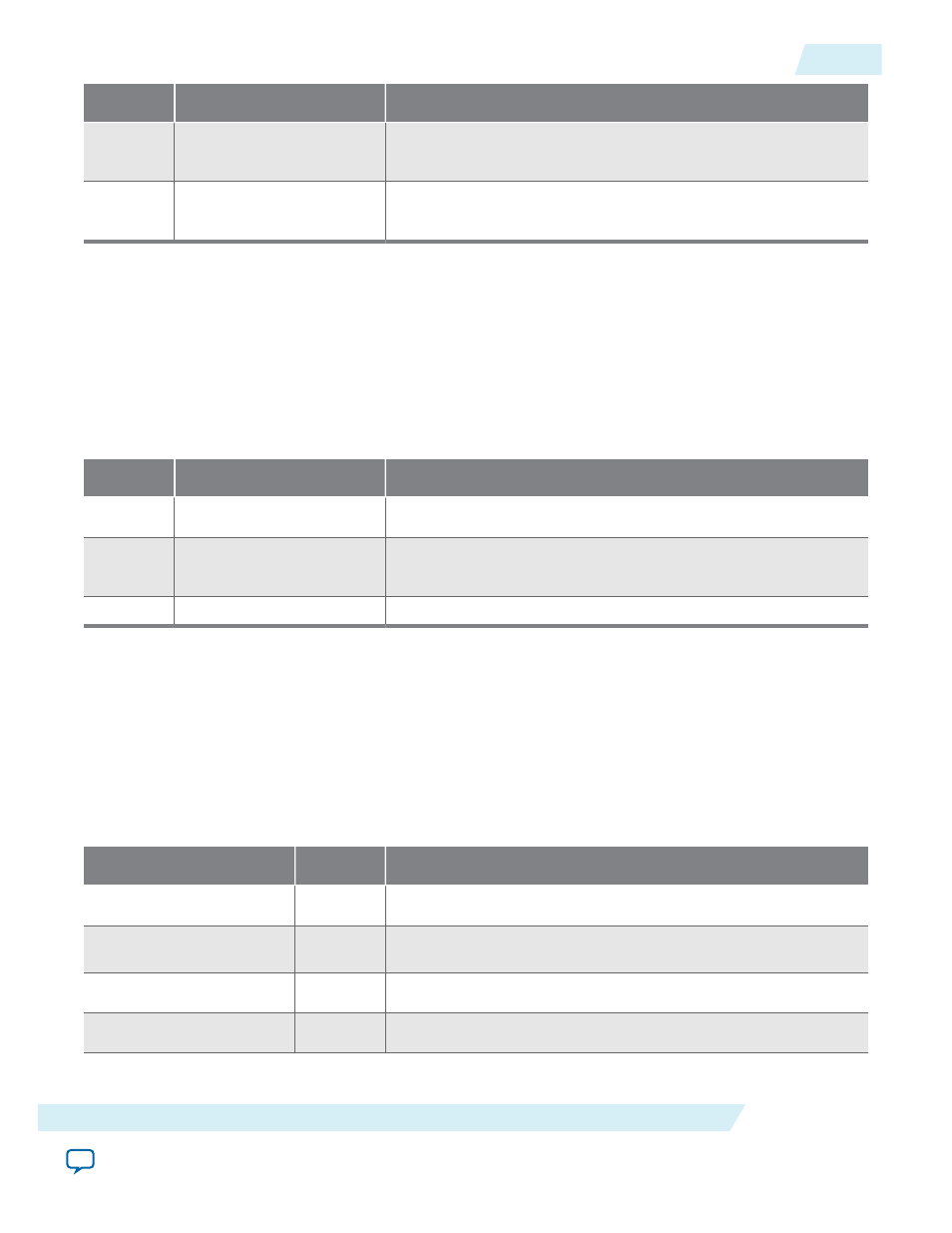

DMA Descriptor Status Bus when Instantiated Separately

Read DMA and Write DMA modules report status to the Descriptor Controller on the

RdDmaTx-

Data_o[31:0]

or

WrDmaTxData_o[31:0]

bus when one of the following trigger events occurs:

• A descriptor is activated

• A descriptor completes successfully

The following table shows the mappings of the triggering events to the DMA descriptor status bus:

Table 5-11: DMA Status Bus

Bits

Name

Description

[31:9]

Reserved.

—

[8]

Done

When asserted, a single DMA descriptor has completed success‐

fully.

[7:0]

Descriptor ID

The ID of the descriptor whose status is being reported.

Descriptor Controller Interfaces when Instantiated Internally

Read Descriptor Controller Avalon-MM Master Port

The Read Descriptor Controller Avalon-MM master port drives the TX Avalon-MM slave port. This port

drives single dword transactions to the Arria 10 Avalon-MM DMA for PCIe. The Read Descriptor

Controller uses this port to write descriptor status to the PCIe domain and possibly to MSI when MSI

messages are enabled.

Table 5-12: Read Descriptor Controller Avalon-MM Master Interface

Signal Name

Direction

Description

RdDCMAddress_o[63:0]

Output

Specifies the address for the read data.

RdDCMByteEnable_

o[3:0]

Output

Specifies which data bytes are valid.

RdDCMReadDataValid_i

Input

When asserted, indicates that the read data is valid.

RdDCMReadData_o[31:0]

Output

Drives the single dword read data.

UG-01145_avmm_dma

2015.05.14

DMA Descriptor Status Bus when Instantiated Separately

5-11

IP Core Interfaces

Altera Corporation