B. additional information, Additional information – Altera Arria 10 Avalon-MM DMA User Manual

Page 127

Additional Information

B

2015.05.14

UG-01145_avmm_dma

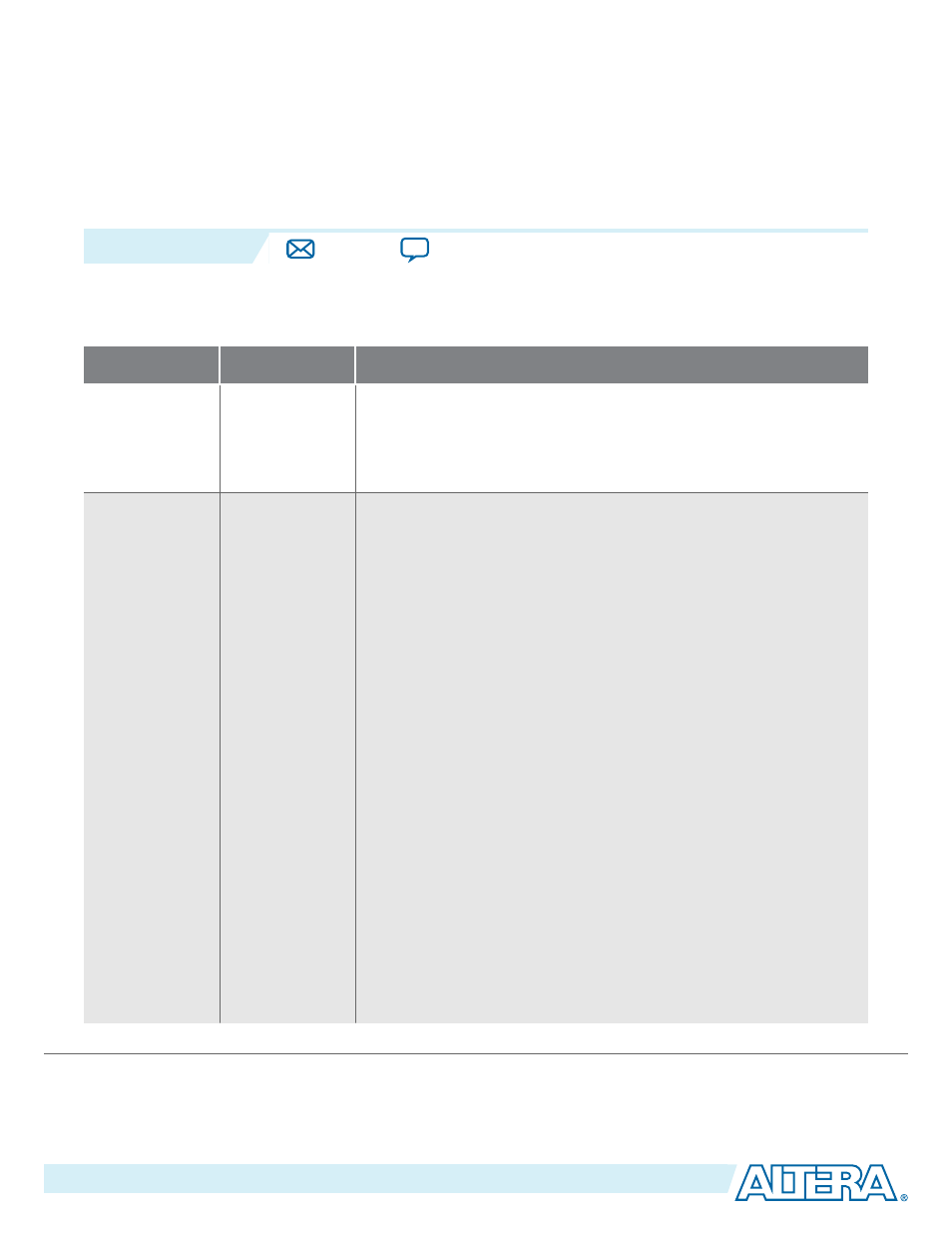

Revision History for the Avalon-MM Interface with DMA

Date

Version

Changes Made

2015.05.14

15.0

Made the following changes to the user guide:

• Added Enable Hard IP Status Bus when using the AVMM

interface parameter in

on page 3-5.

This parameter is available in the IP core v15.0 and later.

2015.05.04

15.0

• Added Enable Altera Debug Master Endpoint (ADME)

parameter to support optional Native PHY register programming

with the Altera System Console.

• Added support for downstream burst read request for a payload of

size up to 4 KBytes, if Enable burst capability for RXM BAR2

port is turned on in the Parameter Editor. Previous maximum

downstream read request payload size was 512 bytes. Refer to

Arria 10 Avalon-MM DMA for PCI Express

• Corrected the allowed value of the Maximum payload size

parameter for Avalon-MM DMA IP core variations, in

• Corrected the supported variations to include Gen3 x2.

• Removed the High and Maximum values for the RX Buffer credit

allocation -performance for received requests parameter. These

values are no longer valid settings. Refer to

page 3-1.

• Enhanced descriptions of channel placement, added fPLL

placement for Gen1 and Gen2 data rates, and added master CGB

location, in

Physical Layout of Hard IP In Arria 10 Devices

page 4-1.

• Reinstated

on page 10-1 chapter.

• Added column for Avalon-ST Interface with SR-IOV variations in

Feature Comparison for all Hard IP for PCI Express IP Cores table

section.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134