Hard ip reconfiguration interface, Hard ip reconfiguration interface -20 – Altera Arria 10 Avalon-MM DMA User Manual

Page 61

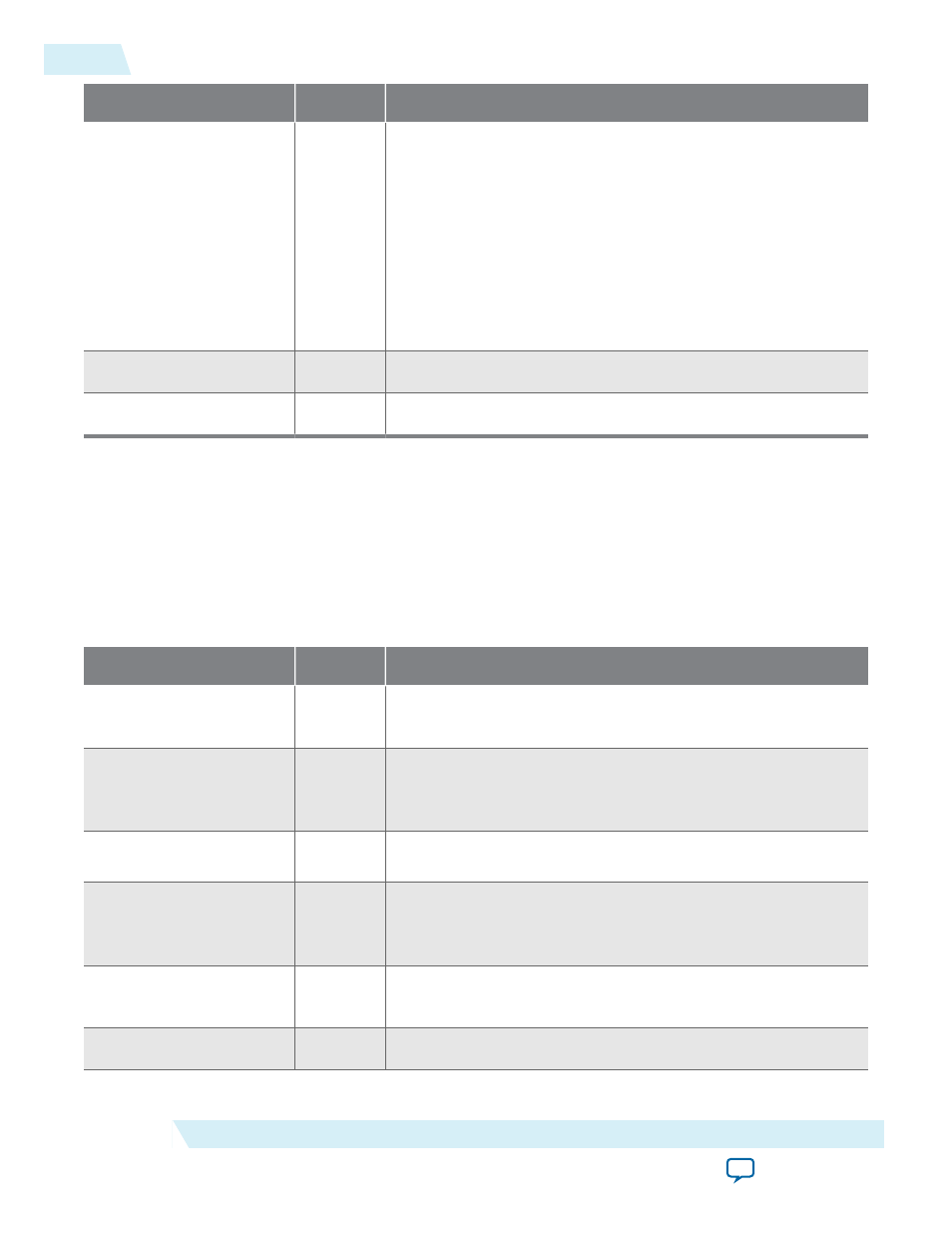

Signal

Direction

Description

MSIControl_o[15:0]

Output

Provides system software control of the MSI messages as defined

in Section 6.8.1.3 Message Control for MSI in the PCI Local Bus

Specification, Rev. 3.0. The following fields are defined:

•

MSIControl_o[15:9]

: Reserved

•

MSIControl_o[8]

: Per-Vector Masking Capable

•

MSIControl_o[7]

: 64-Bit Address Capable

•

MSIControl_o[6:4]

: Multiple Message Enable

•

MSIControl_o[3:1]

: MSI Message Capable

•

MSIControl_o[0]

: MSI Enable

intx_req_i

Input

Legacy interrupt request.

intx_ack_o

Output

Legacy interrupt acknowledge.

Hard IP Reconfiguration Interface

The Hard IP reconfiguration interface is an Avalon-MM slave interface with a 10-bit address and 16-bit

data bus. You can use this bus to dynamically modify the value of configuration registers that are read-

only at run time. To ensure proper system operation, reset or repeat device enumeration of the PCI

Express link after changing the value of read-only configuration registers of the Hard IP.

Table 5-20: Hard IP Reconfiguration Signals

Signal

Direction

Description

hip_reconfig_clk

Input

Reconfiguration clock. The frequency range for this clock is 100–

125 MHz.

hip_reconfig_rst_n

Input

Active-low Avalon-MM reset. Resets all of the dynamic reconfi‐

guration registers to their default values as described in Hard IP

Reconfiguration Registers.

hip_reconfig_

address[9:0]

Input

The 10-bit reconfiguration address.

hip_reconfig_read

Input

Read signal. This interface is not pipelined. You must wait for the

return of the

hip_reconfig_readdata[15:0]

from the current

read before starting another read operation.

hip_reconfig_

readdata[15:0]

Output

16-bit read data.

hip_reconfig_readdata[15:0]

is valid on the

third cycle after the assertion of

hip_reconfig_read

.

hip_reconfig_write

Input

Write signal.

5-20

Hard IP Reconfiguration Interface

UG-01145_avmm_dma

2015.05.14

Altera Corporation

IP Core Interfaces