Altera Arria 10 Avalon-MM DMA User Manual

Page 7

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

• Support for Arria 10 Avalon-MM DMA for PCI Express with either a 128- or 256-bit interface to the

Application Layer. This variant includes an embedded DMA controller for data transfers. The

following table shows the available configurations.

• Easy to use:

• Flexible configuration.

• No license requirement.

• Example designs to get started.

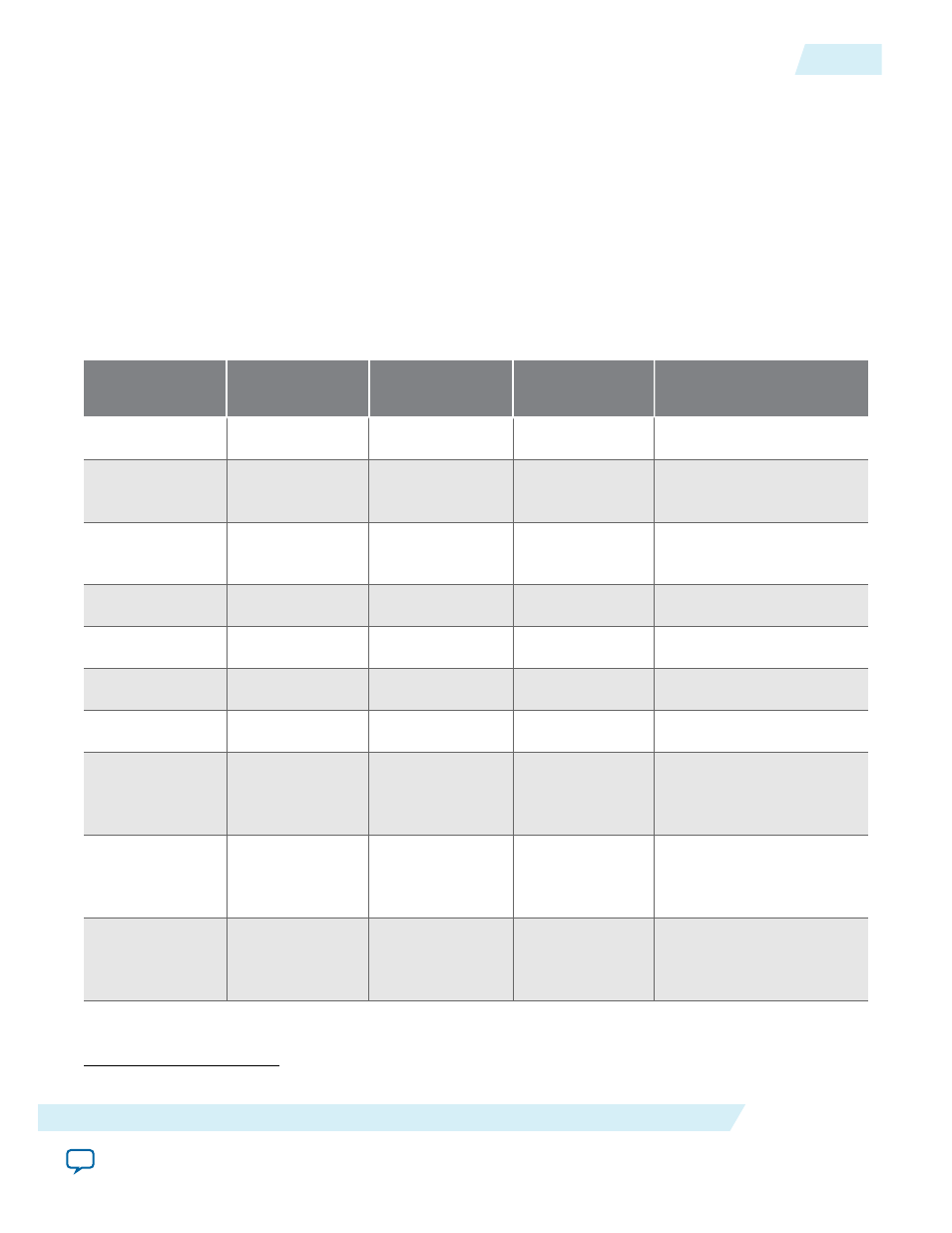

Table 1-2: Feature Comparison for all Hard IP for PCI Express IP Cores

The table compares the features of the four Hard IP for PCI Express IP Cores.

Feature

Avalon-ST Interface

Avalon-MM

Interface

Avalon-MM DMA

Avalon-ST Interface with SR-

IOV

IP Core License Free

Free

Free

Free

Native

Endpoint

Supported

Supported

Supported

Supported

Legacy

Endpoint

(1)

Supported

Not Supported

Not Supported

Not Supported

Root port

Supported

Supported

Not Supported

Not Supported

Gen1

×1, ×2, ×4, ×8

×1, ×2, ×4, ×8

Not Supported

×8

Gen2

×1, ×2, ×4, ×8

×1, ×2, ×4, ×8

×4, ×8

×4, ×8

Gen3

×1, ×2, ×4, ×8

×1, ×2, ×4

×2, ×4, ×8

×2, ×4, ×8

64-bit Applica‐

tion Layer

interface

Supported

Supported

Not supported

Not supported

128-bit

Application

Layer interface

Supported

Supported

Supported

Supported

256-bit

Application

Layer interface

Supported

Not Supported

Supported

Supported

(1)

Not recommended for new designs.

UG-01145_avmm_dma

2015.05.14

Features

1-3

Datasheet

Altera Corporation