Set_command_transaction_mode(), Set_transaction_fifo_max(), Set_transaction_fifo_threshold() – Altera Avalon Verification IP Suite User Manual

Page 109

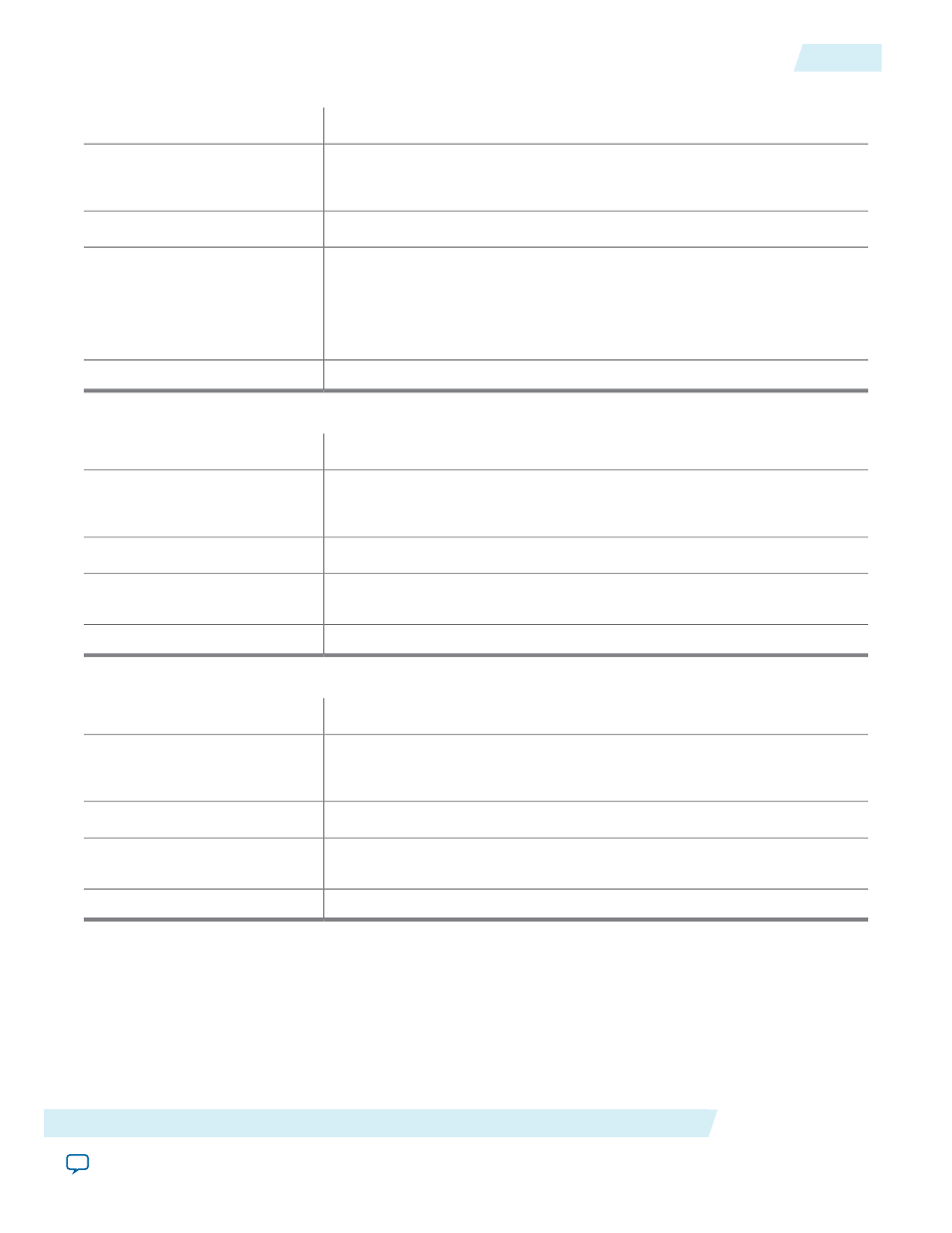

set_command_transaction_mode()

set_command_transaction_mode()

Prototype:

Verilog HDL:

int mode

VHDL:

int mode

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

By default, write burst commands are consolidated into a single command

transaction containing the write data for all burst cycles in that command.

This mode is set when the mode argument equals 0. When the mode

argument is set to 1, the default is overridden. Write burst commands yield

one command transaction per burst cycle.

Description:

Verilog HDL, VHDL

Language support:

set_transaction_fifo_max()

set_transaction_fifo_max()

Prototype:

Verilog HDL:

int level

VHDL:

int level

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

.

Returns:

Sets the maximum transaction level of the FIFO. The event

signal_

transaction_fifo_max

is triggered when this level is exceeded.

Description:

Verilog HDL, VHDL

Language support:

set_transaction_fifo_threshold()

set_transaction_fifo_threshold()

Prototype:

Verilog HDL:

int level

VHDL:

int level

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

.

Returns:

Sets the threshold alert level of the FIFO. The event

signal_transaction_

fifo_threshold

is triggered when this level is exceeded.

Description:

Verilog HDL, VHDL

Language support:

Altera Corporation

Avalon-MM Monitor

7-37

set_command_transaction_mode()