Set_command_idle(), Set_command_init_latency(), Set_command_lock() – Altera Avalon Verification IP Suite User Manual

Page 43

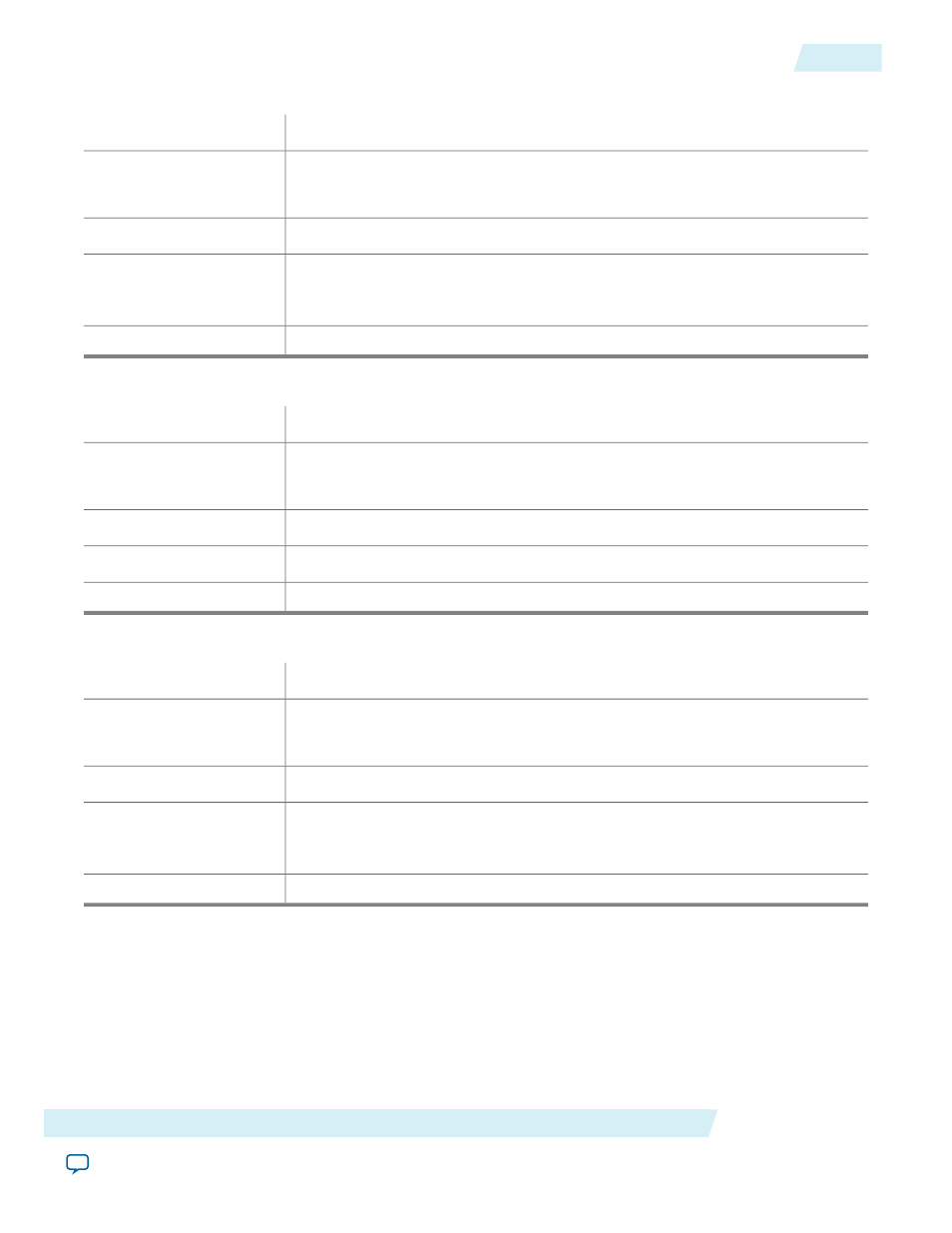

set_command_idle()

void set_command_idle(int idle, int index)

Prototype:

Verilog HDL: int idle, int index

VHDL:

int idle

,

int index

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Sets idle cycles at the end of each transaction cycle. For read commands, idle cycles

are inserted at the end of the command cycle. For burst write commands, idle

cycles are inserted at the end of each write data cycle within the burst.

Description:

Verilog HDL, VHDL

Language support:

set_command_init_latency()

void set_command_init_latency(int cycles)

Prototype:

Verilog HDL:

cycles

VHDL:

cycles

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Sets the number of cycles to postpone the start of a command.

Description:

Verilog HDL, VHDL

Language support:

set_command_lock()

void set_command_lock (bit state)

Prototype:

Verilog HDL: bit state

VHDL:

bit state

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Controls the assertion or deassertion of the lock interface signal. Lock control is

on the transaction boundaries. It is not used when the Avalon-MM Master BFM

is operating in burst mode.

Description:

Verilog HDL, VHDL

Language support:

Altera Corporation

Avalon-MM Master BFM

5-21

set_command_idle()