Get_command_burst_count(), Get_command_burst_cycle(), Get_command_byte_enable() – Altera Avalon Verification IP Suite User Manual

Page 99

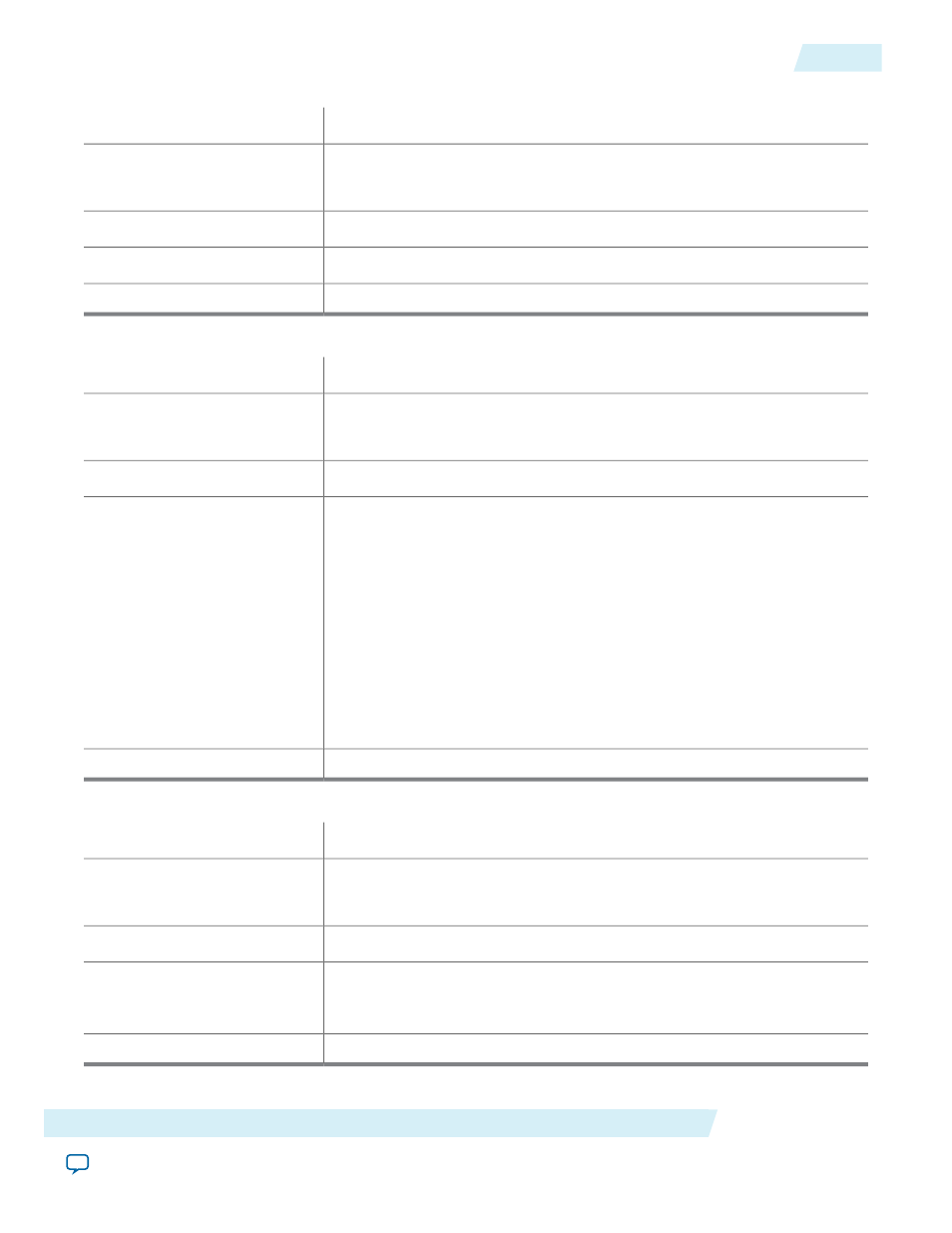

get_command_burst_count()

[AV_BURSTCOUNT_W-1:0] get_command_burst_count()

Prototype:

Verilog HDL: None

VHDL:

command_burst_count

,

bfm_id

,

req_if(bfm_id)

Arguments:

[AV_BURSTCOUNT_W-1:0]

Returns:

Queries the received command descriptor for the transaction burst count.

Description:

Verilog HDL, VHDL

Language support:

get_command_burst_cycle()

int get_command_burst_cycle()

Prototype:

Verilog HDL: None

VHDL:

command_burst_cycle

,

bfm_id

,

req_if(bfm_id)

Arguments:

Int

Returns:

The slave BFM receives and processes write burst commands as a discrete

sequence. The number of commands corresponds to the burst count. A

separate command descriptor is constructed for each write burst cycle,

corresponding to a partially completed burst.

This method returns a burst cycle field specifying the burst cycle that was

active when this descriptor was constructed. This facility enables the

testbench to query partially completed write burst operations. The testbench

can query the write data word on each burst cycle as it arrives. The testbench

can begin to process it immediately. The testbench does not have to wait

until the entire burst has been received. Consequently, it is possible to

perform pipelined write burst processing in the testbench.

Description:

Verilog HDL, VHDL

Language support:

get_command_byte_enable()

bit [AV_NUMSYMBOLS-1:0] get_command_byte_enable (int index)

Prototype:

Verilog HDL:

index

VHDL:

command_byte_enable

,

index

,

bfm_id

,

req_if(bfm_id)

Arguments:

bit[AV_NUMSYMBOLS-1:0]

Returns:

Queries the received command descriptor for the transaction byte enable.

For burst commands with burst count greater than 1, the index selects the

data cycle.

Description:

Verilog HDL, VHDL

Language support:

Altera Corporation

Avalon-MM Monitor

7-27

get_command_burst_count()