Block diagram, Block diagram -2 – Altera Avalon Verification IP Suite User Manual

Page 128

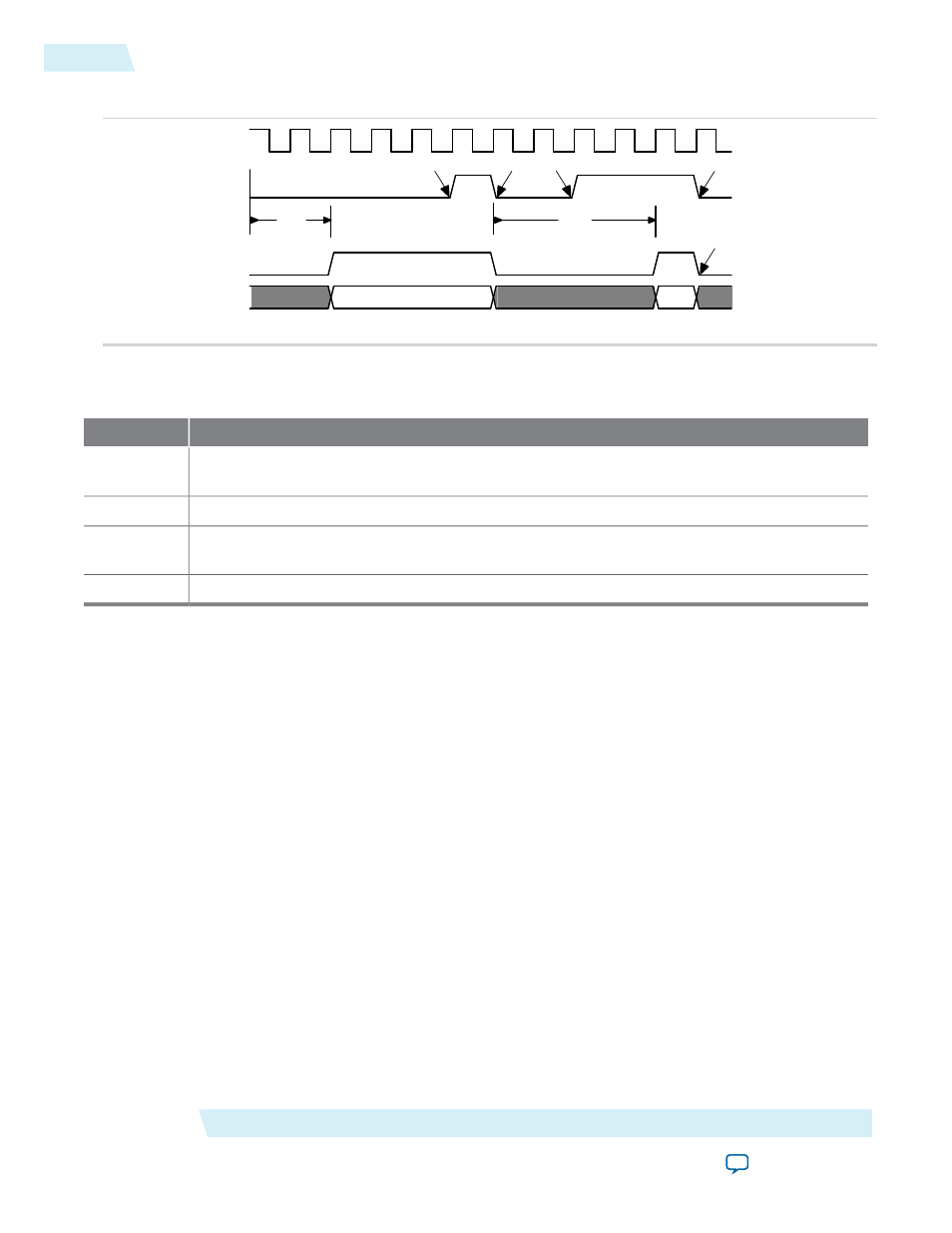

Figure 9-2: Avalon-ST Source and Sink Timing

CLK

ready

valid

data

D1

D2

S

snk_rdya

S

snk_rdyd

S

snk_rdyd

S

tr

S

snk_rdya

T idle

T idle

Table 9-1: Key to Annotations

The following table describes the annotations used in the figure above.

Description

Symbol

The idle time between transactions. This time is reported by the command

get_transaction_

idles

.

T

idle

Signals the sink has asserted

ready

. The event name is

signal_snk_ready_assert

.

S

snk_rdya

Signals the transaction has been received and queued. The event name is

signal_transaction_

received

.

S

tr

Signals the sink is not

ready

. The event name is

signal_snk_ready_deassert

.

S

snk_rdyd

Block Diagram

The following figure provides a block diagram of the Avalon-ST Sink BFM. This figure illustrates that the

BFM includes the following five major blocks:

• Avalon-ST Sink API—Provides methods to get Avalon-ST transactions and control the

ready

signal.

• Transaction Descriptor—Accumulates the fields of an Avalon-ST command.

• Avalon-ST Physical Driver—Asserts and deasserts the

ready

signal to the system interconnect fabric.

• Physical Bus Monitor—Monitors the physical layer and collects transactions.

Avalon-ST Sink BFM

Altera Corporation

Block Diagram

9-2