Altera Avalon Verification IP Suite User Manual

Page 26

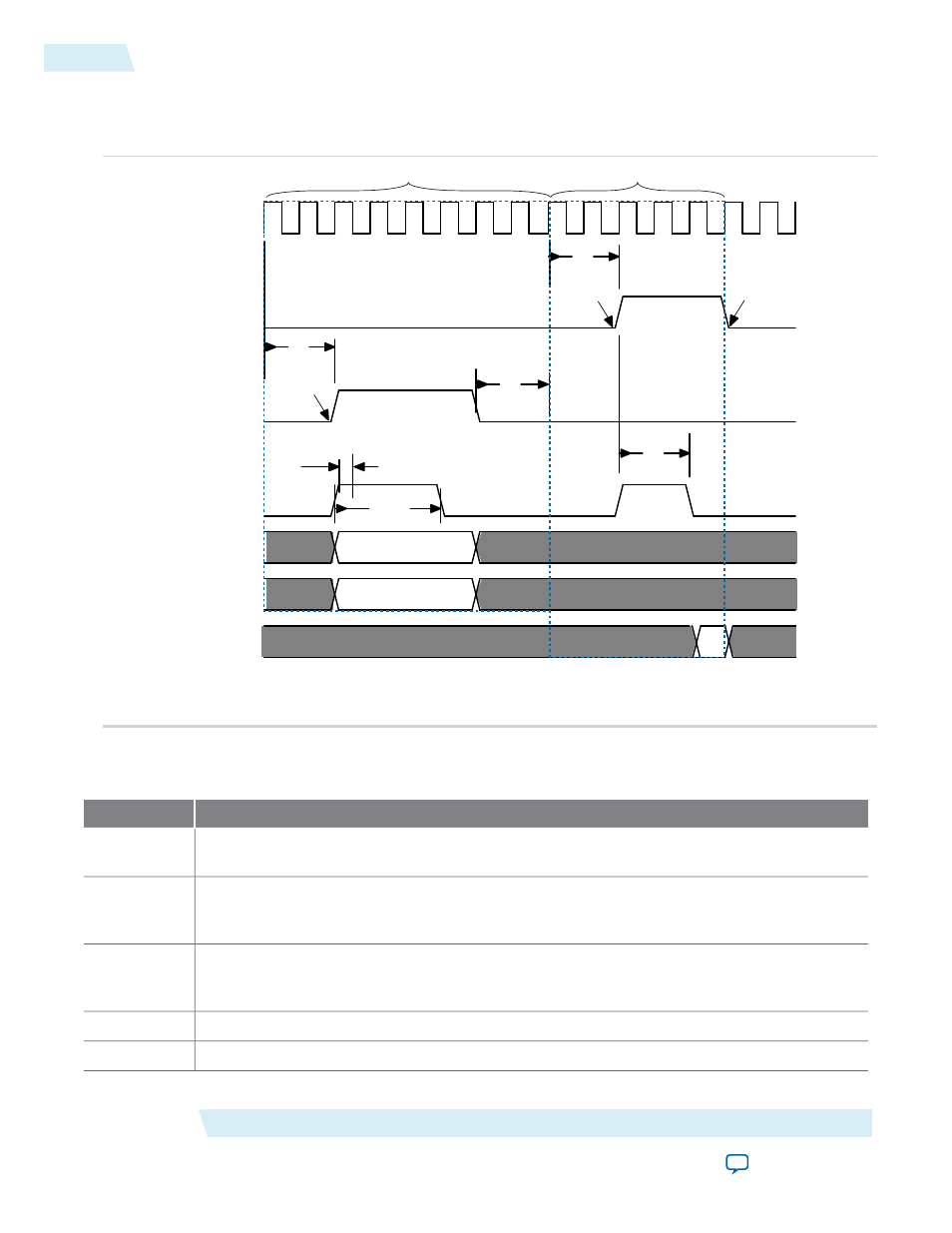

Figure 5-3: Avalon-MM Master Driving Write and Read Transactions with No readdatavalid Signal

The timing in the following figure shows the sequence of events for an Avalon-MM Master BFM. The

Avalon-MM Master BFM drives a write followed by a read when the

readdatavalid

signal is not present.

CLK

read

write

waitrequest

byteenable[3:0]

writedata[31:0]

readdata

D1

D2

T

init

T

init

S

ci_1

T

wt_1

T

wt_2

S

ci_2

S

rc_1,

S

atc

T

wr

transaction5

transaction6

T

idle

Table 5-2: Key to the Annotations

The following table lists the annotations used in this figure.

Description

Symbol

The initial command latency, which is 2 cycles for transactions 1 and 2. This time is set by the

API command

set_command_init_latency

.

T

init

The response wait time, which is 3 cycles. This time is determined by the number of cycles that

the

waitrequest

signal is asserted by the slave.The program gets this value using the

get_

response_wait_time

command.

T

wt_1

The response wait time for the first read, which is 2 cycles. This time is determined by the

number of cycles that the

waitrequest

signal is asserted by the slave.The program gets this

value using the

get_response_wait_time

command.

T

wt_2

waitrequest

is always sampled #1 after the falling edge of

clk

.

T

wr

The idle time after a transaction. This time is set by the command

set_command_idle.

T

idle

Avalon-MM Master BFM

Altera Corporation

Timing

5-4