Testbench – Altera Avalon Verification IP Suite User Manual

Page 15

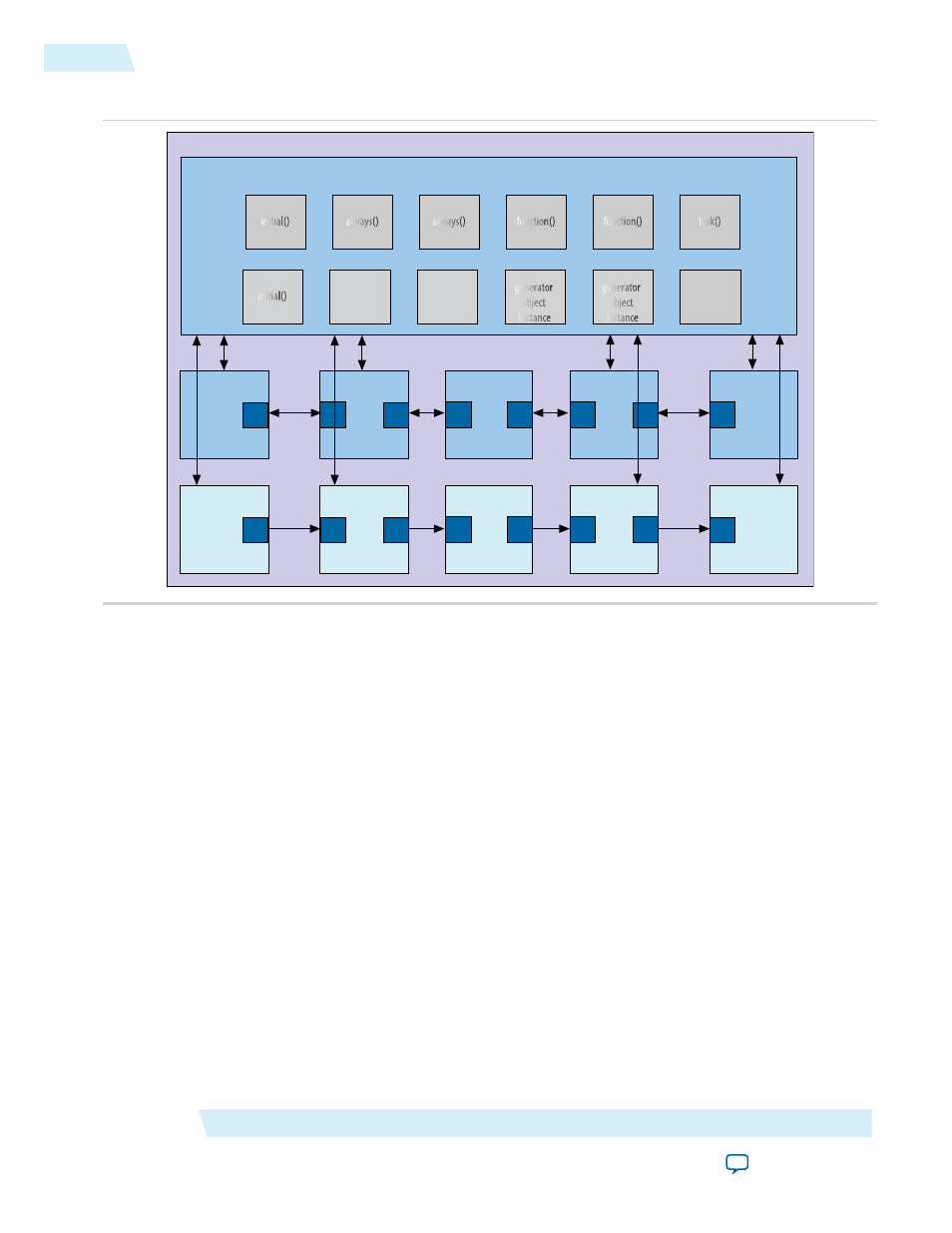

Figure 1-2: Avalon Verification IP Suite Testbench for Avalon-MM and Avalon-ST Interfaces

Testbench

Test Program

Traditional Verilog Implementation

OR

Avalon-MM

read or

write

SystemVerilog with VM

configuration

SRC

Avalon-MM

read or

write

S

Avalon-MM

Slave BFM

S

Avalon-MM

Monitor

Avalon-MM

Master BFM

Avalon-MM

DUT

M

S

S

Avalon-MM

Monitor

Snk

Avalon-ST

Sink BFM

Snk

Avalon-ST

Monitor

Avalon-ST

Source BFM

Avalon-ST

DUT

Src

Src

Snk

Snk

Avalon-ST

Monitor

M

M

M

Src

Src

transactor

generator

object

instance

generator

object

instance

generator

object

instance

generator

object

instance

initial()

initial()

always()

always()

function()

function()

task()

To verify a component with Avalon-MM interfaces, insert a monitor between the master BFM and the slave

interface. To verify a component with Avalon-ST interfaces, insert a monitor between the source BFM and

sink interface. You can insert a second monitor between the slave or sink BFM and the master or source

interface of the DUT. You can inserted monitors anywhere in the system to provide protocol assertion

checking and functional coverage reporting.

The test program drives the stimulus to the DUTs. The test program also determines whether the DUT

behavior is correct, by analyzing the responses. The BFMs translate the test program stimuli. The BFMs

create the signalling for the Avalon-MM and Avalon-ST protocols. The monitors verify Avalon protocol

compliance and provide test coverage reports.

Introduction to Avalon Verification IP Suite

Altera Corporation

Application Example of BFMs

1-4