Avalon-st source api, Avalon-st source api -4 – Altera Avalon Verification IP Suite User Manual

Page 116

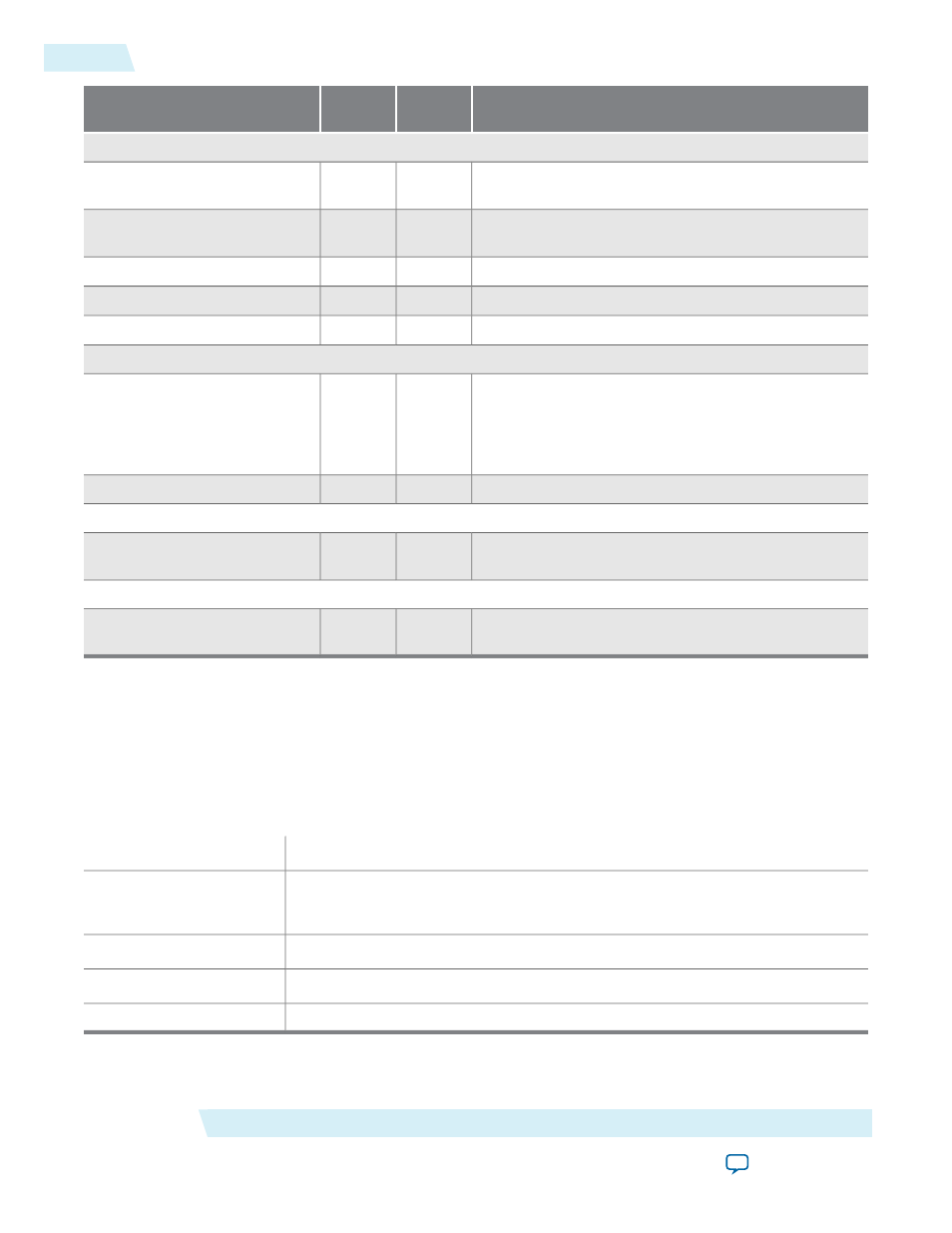

Description

Legal

Values

Default

Value

Parameter

Port Widths

Data symbol width in bits. The symbol width should

be 8 for byte-oriented interfaces.

1–1024

8

Symbol Width

Specifies the number of symbols that are transferred

per beat.

1–1024

4

Number of symbols

Specifies the width of the

channel

signal.

1–32

1

Width of the channel port

Specifies the width of the

error

signal.

1–1024

1

Width of the error port

Specifies the width of the

empty

signal.

1–1024

1

Width of the empty port

Timing Attributes

Specifies the delay between the

ready

and

valid

signals.

For more information about the ready and valid

signals, refer to the Avalon Interface Specification.

0–8

0

Ready latency

Specifies the number of beats per cycle.

1–1024

1

Number of beats per cycle

Channel Attributes

Specifies the maximum number of channels that the

interface supports.

—

1

Max channel number

Miscellaneous

For VHDL BFMs only. Use this option to assign a

unique number to each BFM in the testbench design.

0–1023

0

VHDL BFM ID

Related Information

Avalon-ST Source API

event_max_transaction_queue_size()

event_max_transaction_queue_size()

Prototype:

Verilog HDL: N.A.

VHDL:

bfm_id

Arguments:

void

Returns:

Notifies the testbench that the transaction queue exceeds the maximum level.

Description:

VHDL

Language support:

Avalon-ST Source BFM

Altera Corporation

Avalon-ST Source API

8-4