Avalon-mm monitor assertion checking api, Set_enable_a_address_align_with_data_width(), Avalon-mm monitor assertion checking api -4 – Altera Avalon Verification IP Suite User Manual

Page 76: Set_enable_a_address_align_with_data_width() -4

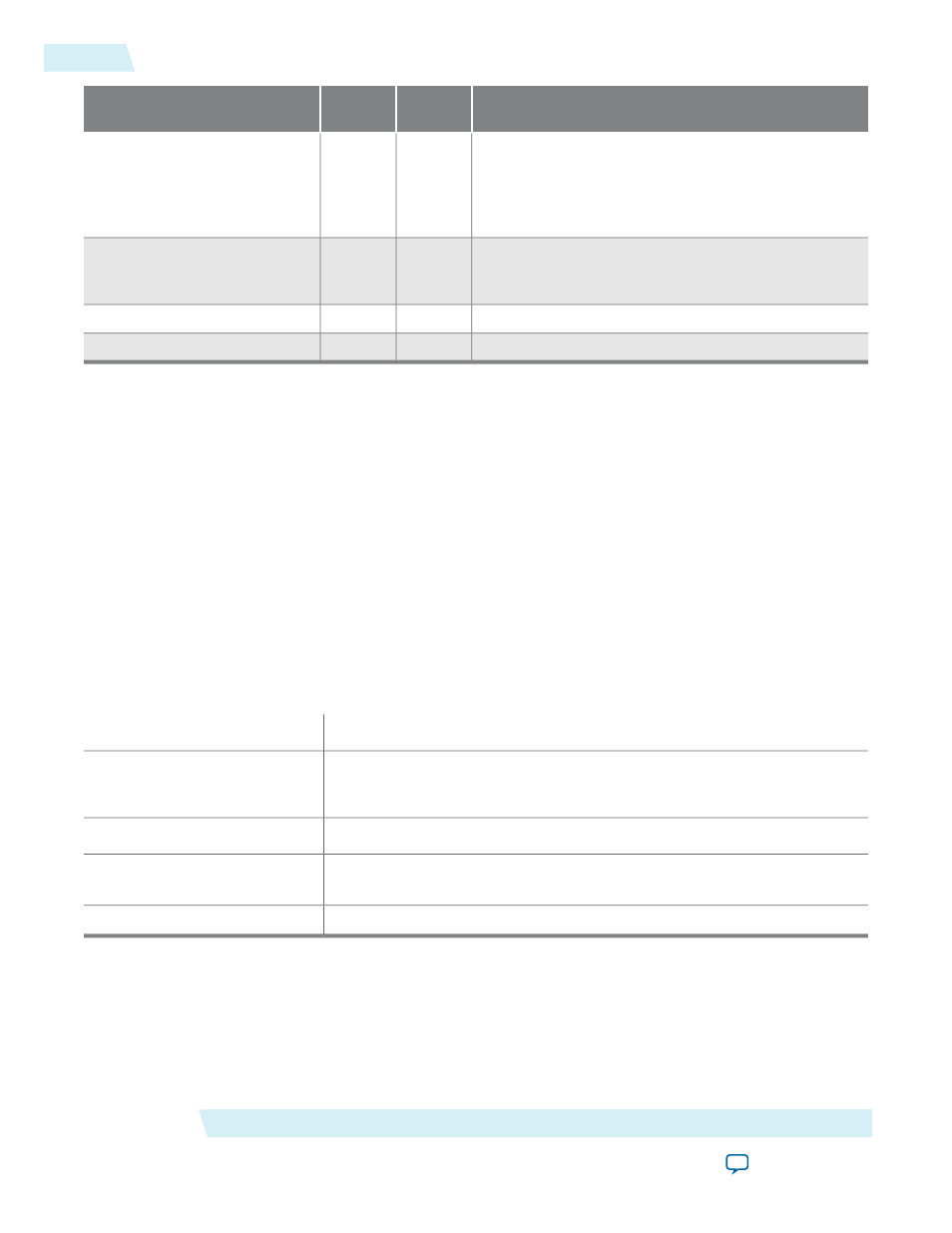

Description

Legal

Values

Default

Value

Parameter

For master interfaces that do not use the

waitrequest

signal. The read wait time indicates the number of

cycles before the master responds to a read. The timing

is as if the master asserted

waitrequest

for this

number of cycles.

N/A

1

Fixed read wait time (cycles)

For master interfaces that do not use the

waitrequest

signal. The write wait time indicates the number of

cycles before the master accepts a write.

N/A

0

Fixed write wait time (cycles)

Specifies whether to turn on the register stage.

On/Off

Off

Registered waitrequest

Specifies whether to register incoming signals.

On/Off

Off

Registered Incoming Signals

Avalon-MM Monitor Assertion Checking API

Assertion checking uses the

enable_waitrequest_timeout

method to verify that

waitrequest

is asserted

for fewer cycles than the

waitrequest

timeout period. If the timeout period is violated, an error message

displays on the simulation console. Error flags are also displayed in the waveform viewer.

By default all assertions are enabled. However, depending on the parameterization of the Avalon-MM

interface, some assertions are automatically disabled. For example, you might have to turn off some assertion

checking to avoid the monitors generating error messages when injecting protocol errors. Protocol errors

are typically injected to test the Avalon-MM component’s error handling capability.

The names of all methods that enable assertions begin with

set_enable_a

. By default, if your testbench

includes the Avalon-MM monitor, the checking function is enabled. You can disable checking with the

DISABLE_ALTERA_AVALON_SIM_SVA

macro.

set_enable_a_address_align_with_data_width()

set_enable_a_address_align_with_data_width()

Prototype:

Verilog HDL:

Boolean

VHDL: N.A.

Arguments:

void

Returns:

Enables an assertion that ensures the byte address that the master uses is

aligned with the data width.

Description:

Verilog HDL

Language support:

Avalon-MM Monitor

Altera Corporation

Avalon-MM Monitor Assertion Checking API

7-4