Altera Integer Arithmetic IP User Manual

Page 103

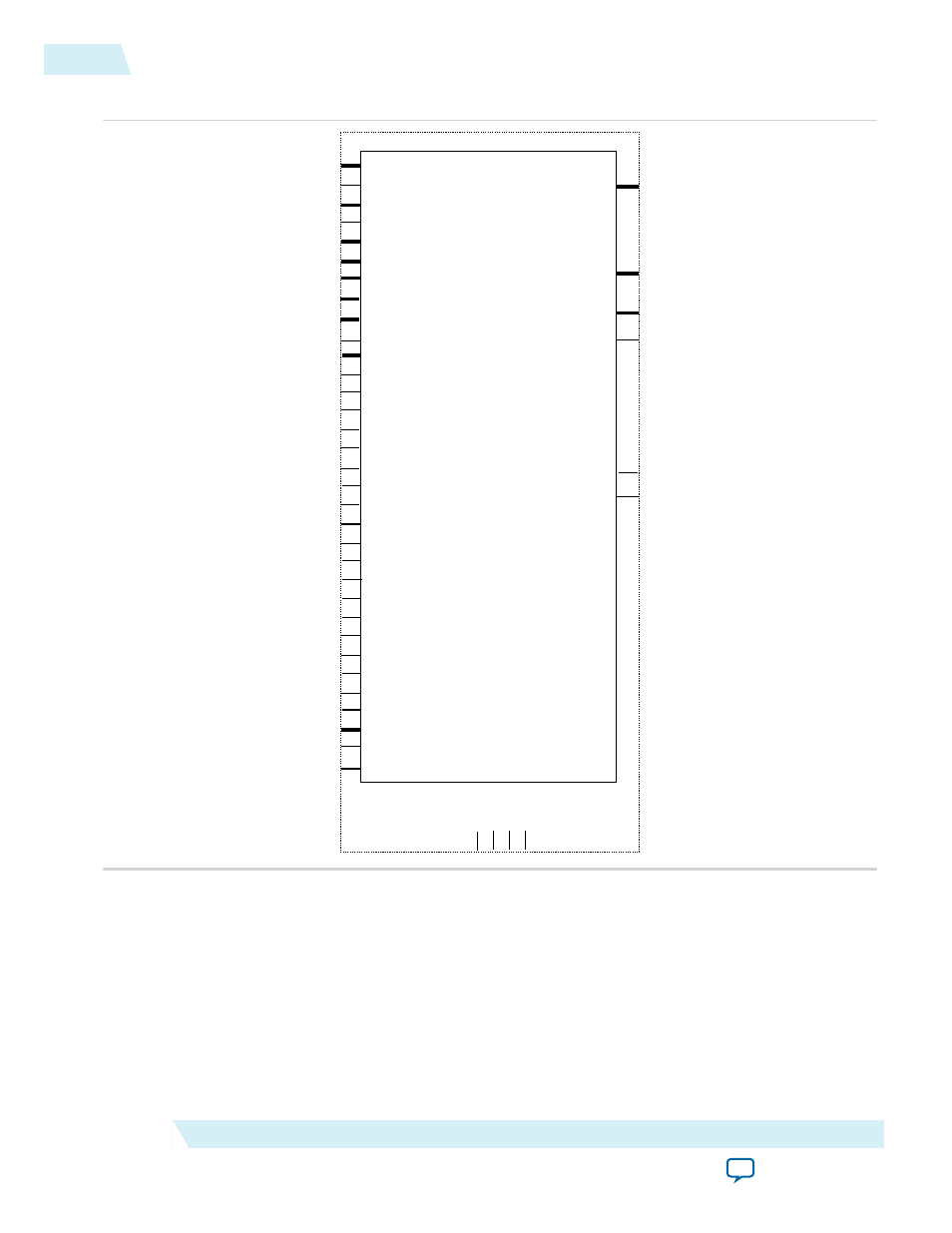

Figure 9-1: ALTMULT_ADD Ports

dataa[]

inst

ALTMULT_ADD

datab[]

signa

scanouta[]

signb

scanoutb[]

result[]

overflow

mult_is_saturated

chain_out_sat_overflow

aclr0

aclr1

aclr2

aclr3

datac[]

coefsel1[]

addnsub1

addnsub3

clock0

ena0

clock1

ena1

clock2

ena2

clock3

ena3

output_round

output_saturate

chainout_round

chainout_saturate

zero_chainout

accum_sload

zero_loopback

chainin[]

shift_right

rotate

addsub1_round

addsub3_round

mult[]_round

mult[]_saturation

coefsel2[]

coefsel3[]

coefsel0[]

A multiplier-adder accepts pairs of inputs, multiplies the values together and then adds to or subtracts

from the products of all other pairs.

The ALTMULT_ADD megafunction also offers many variations in dedicated DSP block circuitry. Data

input sizes of up to 18 bits are accepted. Because the DSP blocks allow for one or two levels of 2-input add

or subtract operations on the product, this function creates up to four multipliers.

Stratix III and Stratix IV device families use two MAC blocks (mac_mult and mac_out) to form DSP

operations, multiply and add. For Stratix V devices, the multiplier blocks and adder/accumulator block is

combined in a single MAC block.

9-2

ALTMULT_ADD (Multiply-Adder)

UG-01063

2014.12.19

Altera Corporation

ALTMULT_ADD (Multiply-Adder)