Pre-load constant, Double accumulator, Pre-load constant -9 – Altera Integer Arithmetic IP User Manual

Page 62: Double accumulator -9

The following lists the advantages of systolic register implementation:

• Reduces DSP resource usage

• Enables efficient mapping in the DSP block using the chain adder structure

The systolic delay implementation is only available for the following pre-adder modes:

• Pre-adder coefficient mode

• Pre-adder simple mode

• Pre-adder constant mode

Pre-load Constant

The pre-load constant controls the accumulator operand and complements the accumulator feedback.

The valid

LOADCONST_VALUE

ranges from 0–64. The constant value is equal to 2

N

, where N =

LOADCONST_VALUE

. When the

LOADCONST_VALUE

is set to 64, the constant value is equal to 0. This function

can be used as biased rounding.

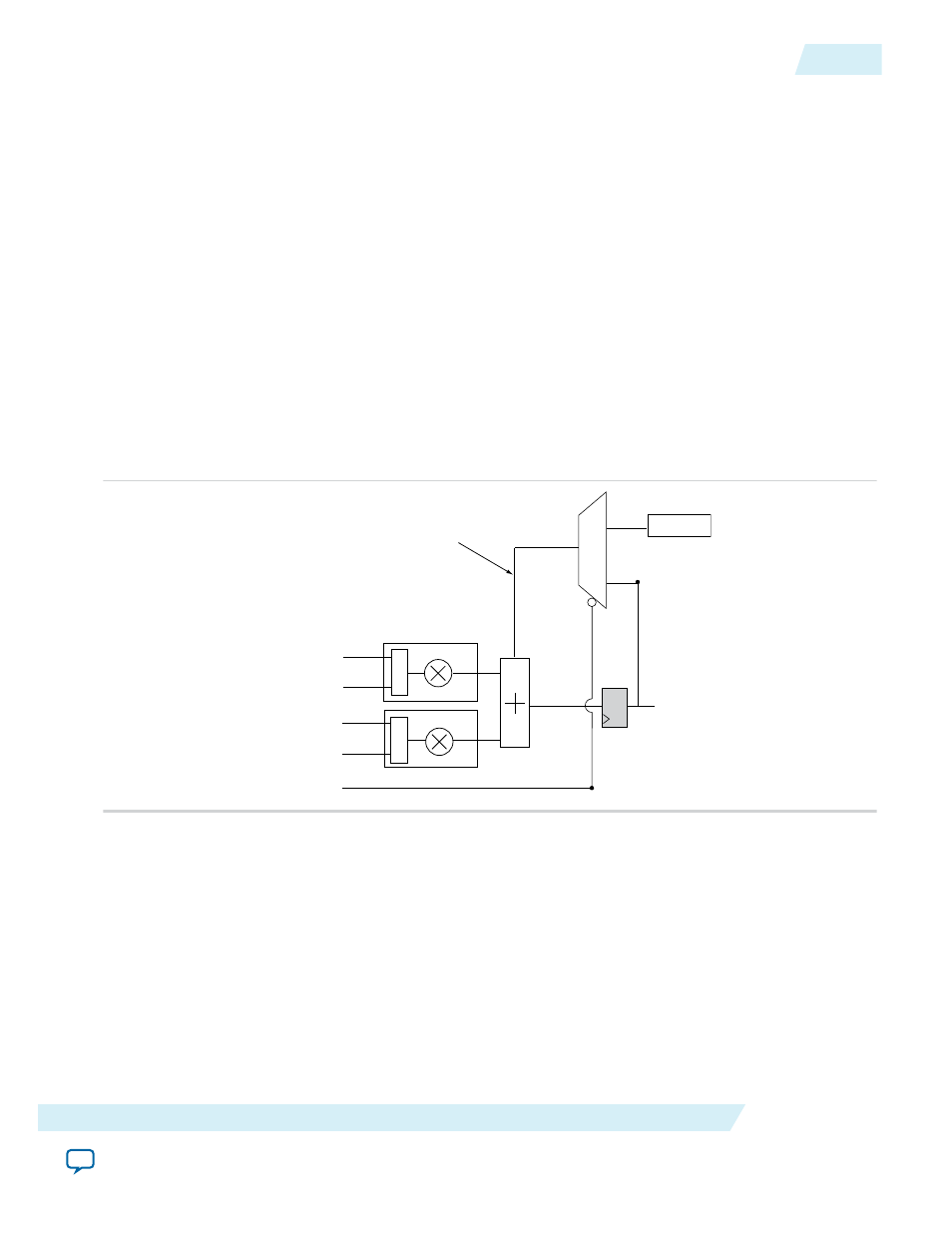

The following figure shows the pre-load constant implementation.

Figure 6-11: Pre-load Constant

a0

b0

a1

b1

Mult0

Mult1

Accumulator feedback

accum_sload

constant

result

+/-

+/-

Refer to the following megafunctions in this user guide for other multiplier implementations:

•

ALTMULT_ACCUM (Multiply-Accumulate)

•

ALTMEMMULT (Memory-based Constant Coefficient Multiplier)

•

Double Accumulator

The double accumulator feature adds an additional register in the accumulator feedback path. The double

accumulator register follows the output register, which includes the clock, clock enable, and aclr. The

additional accumulator register returns result with a one-cycle delay. This feature enables you to have two

accumulator channels with the same resource count.

UG-01063

2014.12.19

Pre-load Constant

6-9

ALTERA_MULT_ADD (Multiply-Adder)

Altera Corporation