Vhdl library_use declaration, Altmult_add ports, Vhdl library_use declaration -12 – Altera Integer Arithmetic IP User Manual

Page 113: Altmult_add ports -12

To view the VHDL component declaration for the megafunction, refer to the VHDL Design File (.vhd)

altera_mf_components.vhd in the

<Quartus II installation directory>\libraries\vhdl\altera_mf

directory.

VHDL LIBRARY_USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component Declaration.

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

ALTMULT_ADD Ports

The following tables list the input and output ports for the ALTMULT_ADD megafunction.

Note: For Arria V, Cyclone V, and Stratix V devices, each register can only select between two asynchro‐

nous signals (

ACLR0

,

ACLR1

) and three clock/enable pairs (

CLOCK0/ENA0

,

CLOCK1/ENA1

,

CLOCK2/

ENA2

).

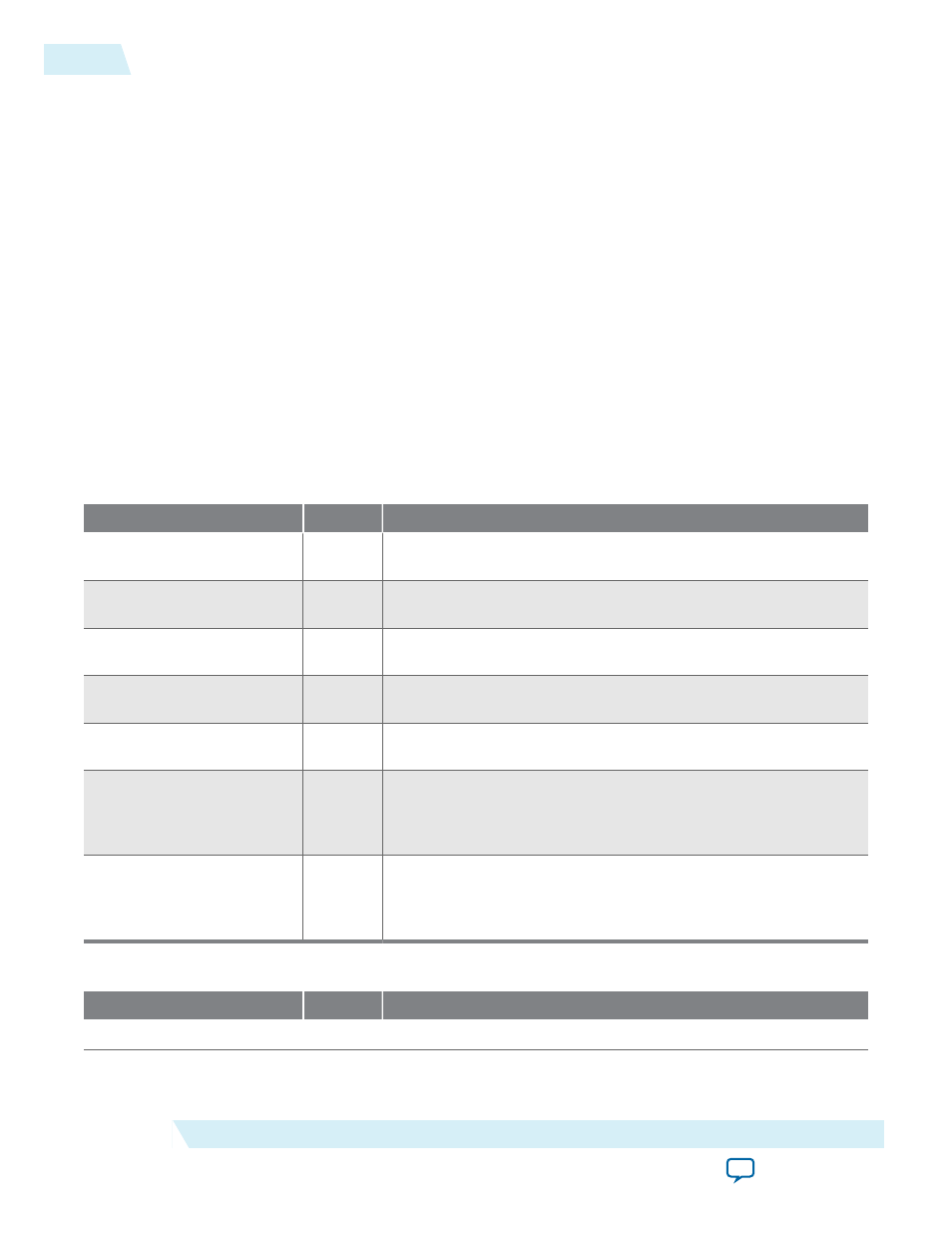

Table 9-2: ALTMULT_ADD Megafunction Input Ports

Port Name

Required

Description

dataa[]

Yes

Data input to the multiplier. Input port

[NUMBER_OF_

MULTIPLIERS * WIDTH_A - 1..0]

wide.

datab[]

Yes

Data input to the multiplier. Input port

[NUMBER_OF_

MULTIPLIERS * WIDTH_B - 1..0]

wide.

clock[]

No

Clock input port

[0..3]

to the corresponding register. This port

can be used by any register in the megafunction.

aclr[]

No

Input port

[0..3]

. Asynchronous clear input to the

corresponding register.

ena[]

No

Input port

[0..3]

. Clock enable for the corresponding clock[]

port.

signa

No

Specifies the numerical representation of the

dataa[]

port. If the

signa

port is high, the multiplier treats the

dataa[]

port as a

signed two's complement number. If the

signa

port is low, the

multiplier treats the

dataa[]

port as an unsigned number.

signb

No

Specifies the numerical representation of the

datab[]

port. If the

signb

port is high, the multiplier treats the

datab[]

port as a

signed two's complement number. If the

signb

port is low, the

multiplier treats the

datab[]

port as an unsigned number.

Table 9-3: ALTMULT_ADD Megafunction Input Ports (Stratix III and Stratix IV Devices Only)

Port Name

Required

Description

Ports Available in Stratix III and Stratix IV devices only

9-12

VHDL LIBRARY_USE Declaration

UG-01063

2014.12.19

Altera Corporation

ALTMULT_ADD (Multiply-Adder)