Verilog hdl prototype, Vhdl component declaration, Verilog hdl prototype -2 – Altera Integer Arithmetic IP User Manual

Page 27: Vhdl component declaration -2

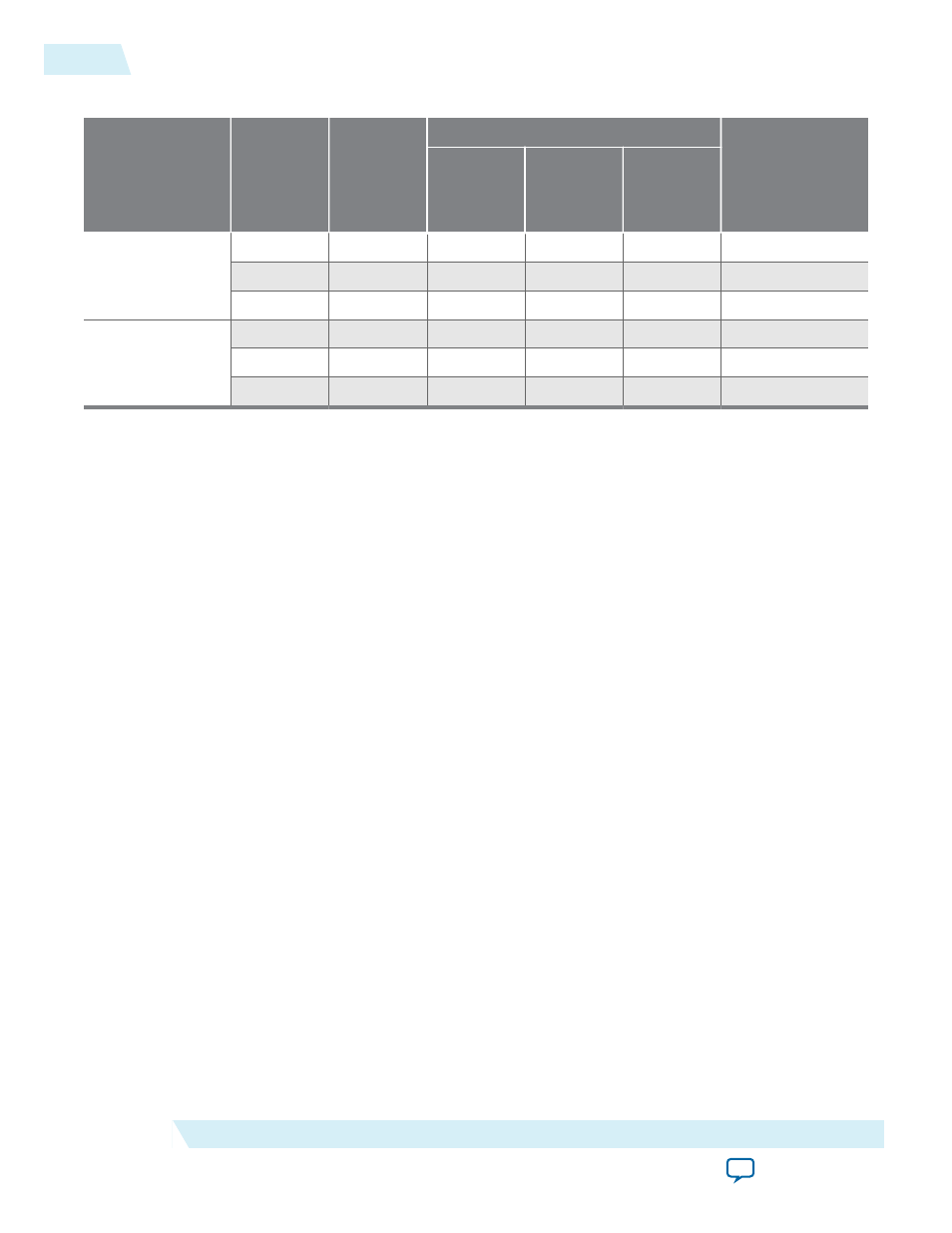

Table 3-1: LPM_DIVIDE Resource Utilization and Performance

Device family

Input data

width

Output

latency

Logic Usage

f

MAX

(MHz)

Adaptive

Look-Up

Table (ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

10

1

131

0

70

133

30

5

1017

0

635

71

64

10

4345

0

2623

41

Stratix IV

10

1

131

0

70

138

30

5

1018

0

642

82

64

10

4347

0

2634

48

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) lpm.v in the <Quartus II

installation directory>\eda\synthesis directory.

module lpm_divide ( quotient, remain, numer, denom, clock, clken, aclr);

parameter lpm_type = "lpm_divide";

parameter lpm_widthn = 1;

parameter lpm_widthd = 1;

parameter lpm_nrepresentation = "UNSIGNED";

parameter lpm_drepresentation = "UNSIGNED";

parameter lpm_remainderpositive = "TRUE";

parameter lpm_pipeline = 0;

parameter lpm_hint = "UNUSED";

input clock;

input clken;

input aclr;

input [lpm_widthn-1:0] numer;

input [lpm_widthd-1:0] denom;

output [lpm_widthn-1:0] quotient;

output [lpm_widthd-1:0] remain;

endmodule

VHDL Component Declaration

The VHDL component declaration is located in the VHDL Design File (.vhd) LPM_PACK.vhd in the

<Quartus II installation directory>

\libraries\vhdl\lpm

directory.

component LPM_DIVIDE

generic (LPM_WIDTHN : natural;

LPM_WIDTHD : natural;

LPM_NREPRESENTATION : string := "UNSIGNED";

LPM_DREPRESENTATION : string := "UNSIGNED";

LPM_PIPELINE : natural := 0;

LPM_TYPE : string := L_DIVIDE;

LPM_HINT : string := "UNUSED");

port (NUMER : in std_logic_vector(LPM_WIDTHN-1 downto 0);

3-2

Verilog HDL Prototype

UG-01063

2014.12.19

Altera Corporation

LPM_DIVIDE (Divider)