Understanding the simulation results, Understanding the simulation results -6 – Altera Integer Arithmetic IP User Manual

Page 79

Understanding the Simulation Results

The following settings are observed in this example:

• The data_in[] and coeff_in[] input widths are both set to 8 bits

• The output port, result[] is set to a width of 16 bits

• The initial coefficient is 2

• The output latency is fixed to seven clock cycles based on the input widths set

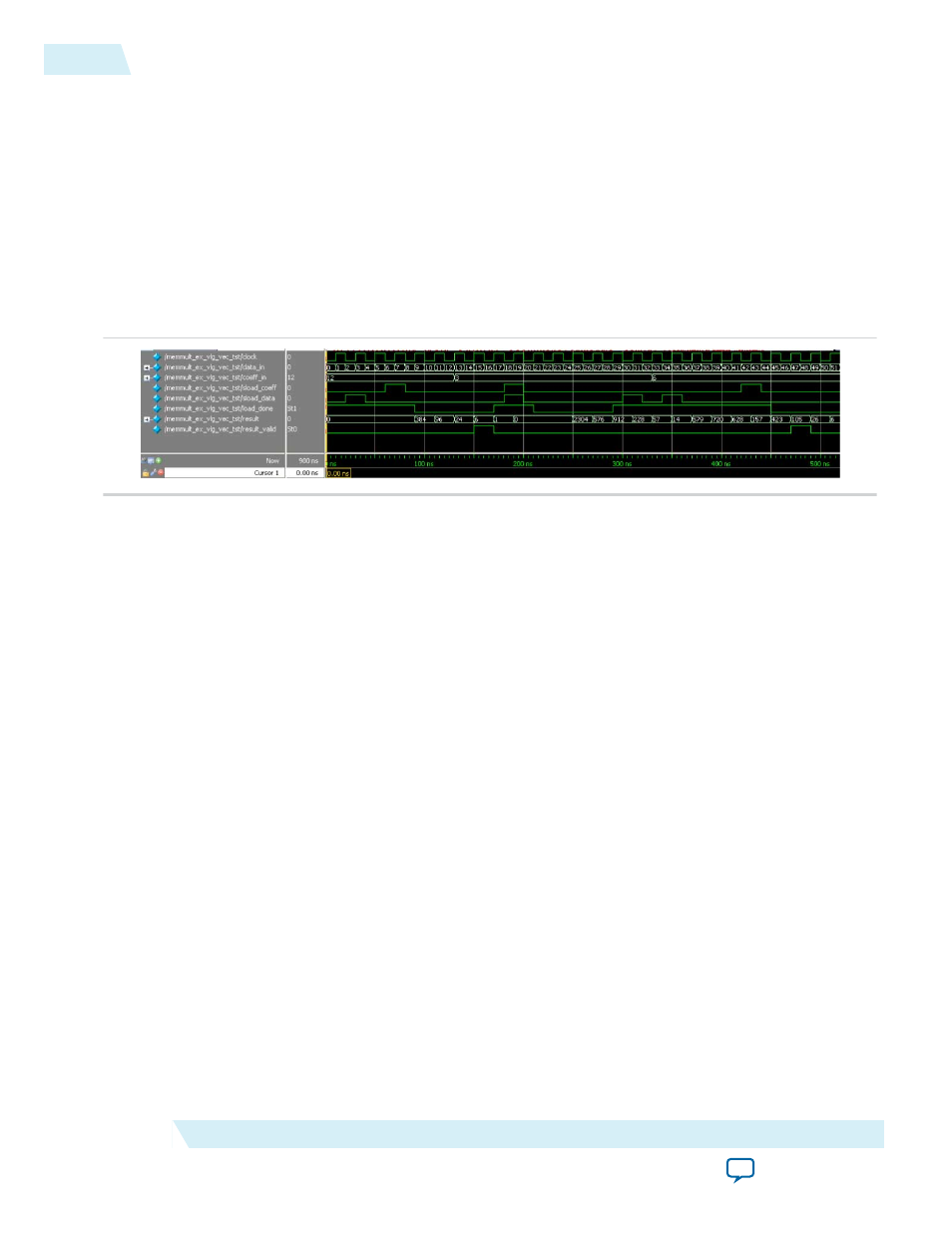

• The following figure shows the expected simulation results in the ModelSim-Altera software.

Figure 7-2: ALTMEMMULT Simulation Results

This design example implements a multiplier for unsigned 8-bit numbers. If the value of the

MAX_CLOCK_CYCLES_PER_RESULT parameter is more than 1, the sload_data signal indicates a new

multiplication and the result_valid signal indicates the validity of the multiplication result.

If the value of the MAX_CLOCK_CYCLES_PER_RESULT parameter is 1, the sload_data signal is not

used and every positive clock edge starts a new multiplication.

In this design example, with the MAX_CLOCK_CYCLES_PER_RESULT parameter set to 4, the design

requires no less than four clock cycles to compute the multiplication. The sload_data signal is used to

indicate a new multiplication.

Altera recommends that you do not pull the sload_data signal high during the four clock cycles when the

multiplication is taking place to avoid getting unpredictable results.

The megafunction only receive new inputs after four clock cycles. With the TOTAL_LATENCY

parameter set to 7, all multiplication results require seven clock cycles to appear at the result[] port. The

COEFFICIENT0 parameter holds the value of the first fixed coefficient, which is set to 2

(COEFFICIENT0=2) for this design example. The megafunction uses the latest coefficient value for every

multiplication.

The sload_data signal asserts when a new coefficient value is written into the register. The load_done

signal pulls low one clock cycle after the sload_data signal deasserts. When the load_done signal is low,

the new coefficient value is reprogrammed into the RAM look-up table. Until the load_done signal pulls

high, no other coefficient value can be loaded into the memory (regardless of whether the sload_data

signal asserts anytime in between). The load_done signal asserts when programming completes.

The load time required to write a new coefficient value into the register is the same for any instance of the

ALTMEMMULT megafunction. However, the load time can vary depending on the size of the RAM used.

The following figure shows the simulation results for the multiplication implementation with coefficient

of 2.

7-6

Understanding the Simulation Results

UG-01063

2014.12.19

Altera Corporation

ALTMEMMULT (Memory-based Constant Coefficient Multiplier)