Resource utilization and performance, Verilog hdl prototype, Resource utilization and performance -4 – Altera Integer Arithmetic IP User Manual

Page 141: Verilog hdl prototype -4

Resource Utilization and Performance

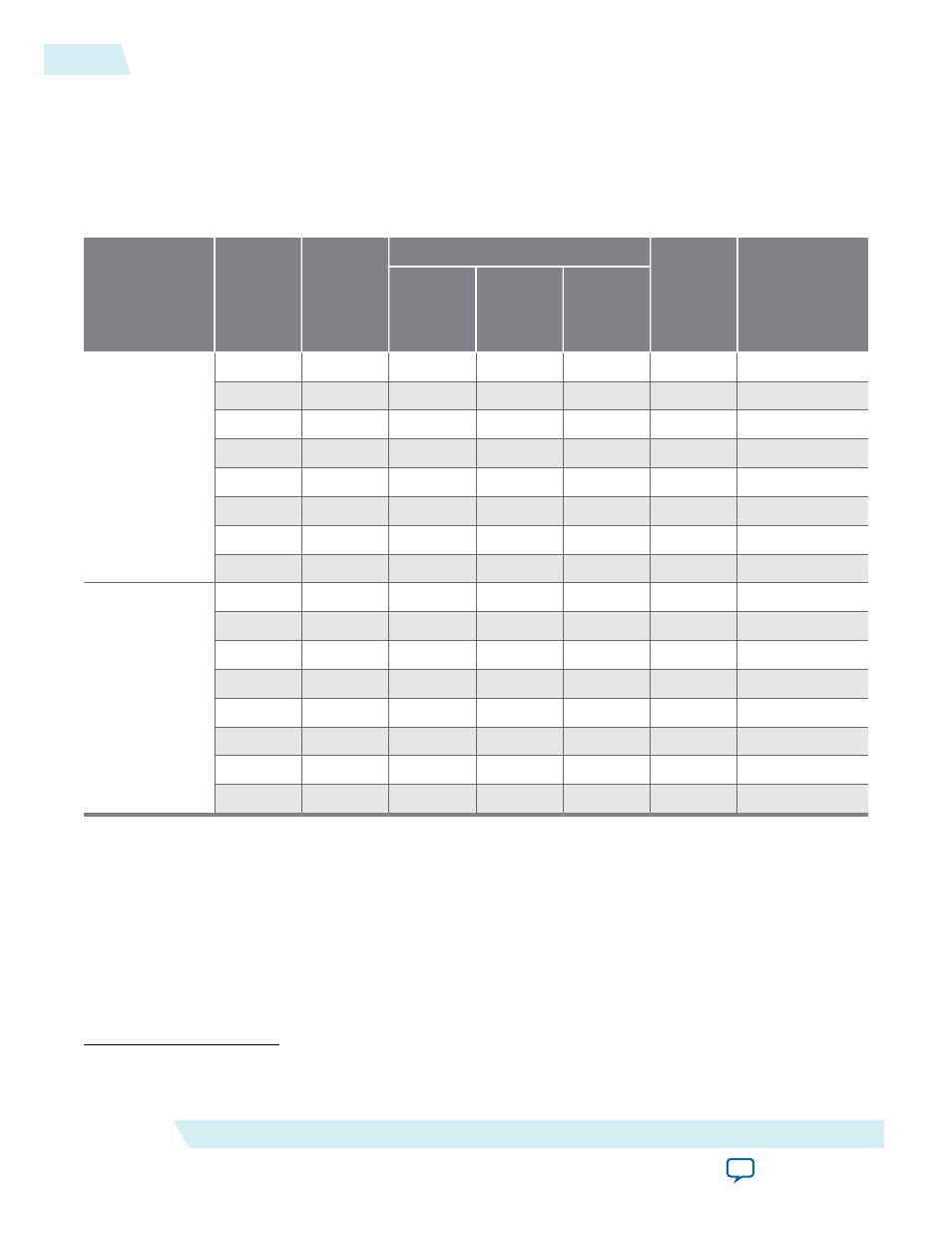

The following table provides resource utilization and performance information for the

ALTMULT_COMPLEX megafunction.

Table 10-1: ALTMULT_COMPLEX Resource Utilization and Performance

Device family

Input data

width

Output

latency

Logic Usage

18-bit DSP

f

MAX

(MHz)

(7)

Adaptive

Look-Up

Table

(ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

8

0

0

0

0

4

529

16

0

0

0

0

4

531

32

0

73

0

37

16

291

64

0

73

0

37

16

292

8

14

19

10

10

4

492

16

14

19

10

10

4

502

32

14

91

8

47

16

265

64

14

91

8

47

16

268

Stratix IV

8

0

0

0

0

4

487

16

0

0

0

0

4

487

32

0

73

0

37

16

293

64

0

73

0

37

16

293

8

14

19

10

10

4

489

16

14

20

10

10

4

493

32

14

91

8

47

16

292

64

14

91

8

47

16

291

Verilog HDL Prototype

The following Verilog HDL prototype is located in the Verilog Design File (.v) altera_mf.v in the

<Quartus II installation directory>\eda\synthesis directory.

module altmult_complex

# (parameter intended_device_family = "unused",

parameter implementation_style = "AUTO",

parameter pipeline = 4,

(7)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

10-4

Resource Utilization and Performance

UG-01063

2014.12.19

Altera Corporation

ALTMULT_COMPLEX (Complex Multiplier)