Altera Integer Arithmetic IP User Manual

Page 42

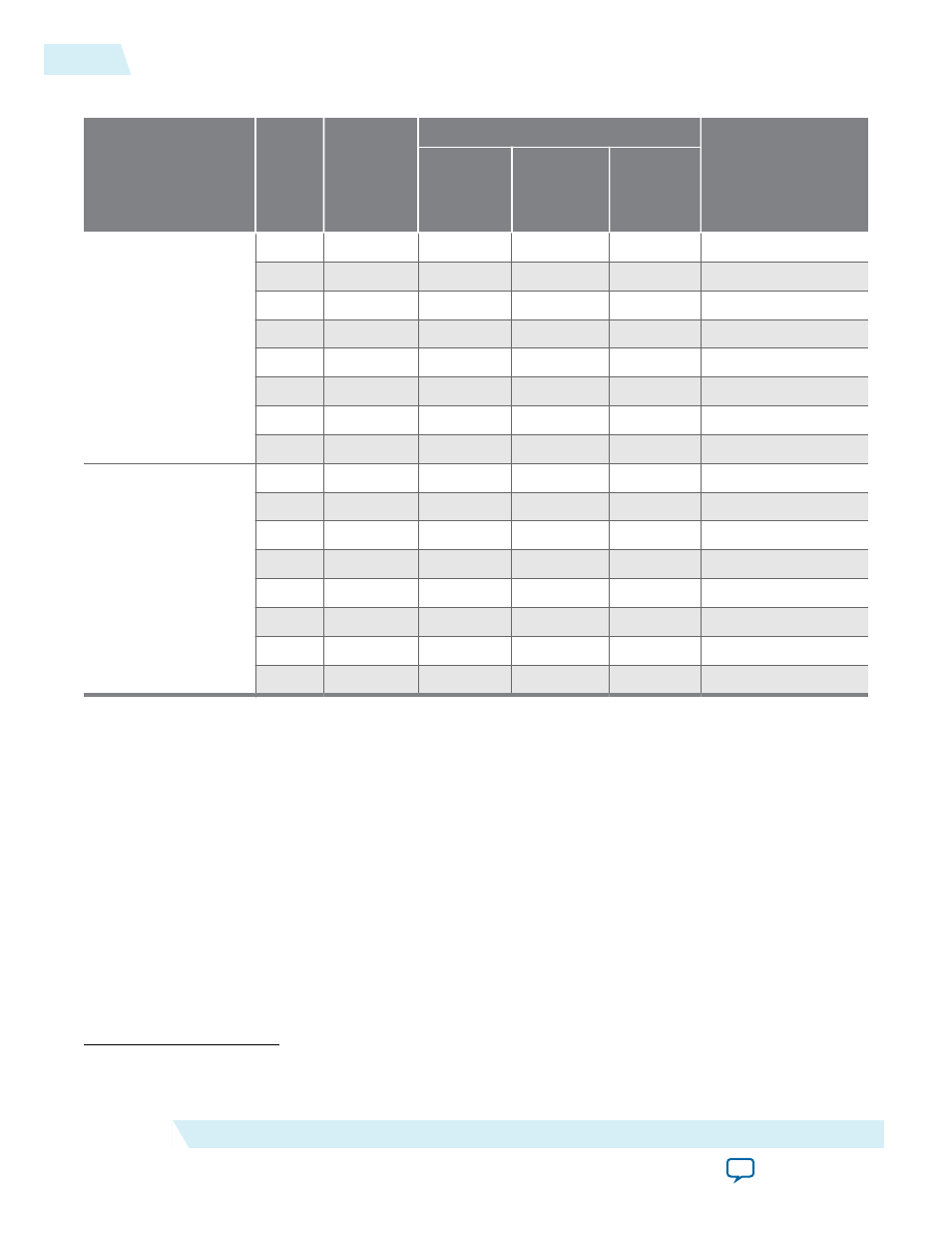

Table 5-2: ALTECC Resource Utilization and Performance for Stratix III Devices

Configuration

Input

data

width

Output

latency

Logic Usage

f

MAX

(MHz)

Adaptive

Look-Up

Table

(ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

ALTECC_

ENCODER

12

0

8

0

4

1161

29

0

21

0

13

1076

32

0

19

0

12

979

64

0

40

0

27

758

12

2

8

30

19

1188

29

2

20

65

36

1021

32

2

19

71

40

1013

64

2

39

136

79

926

ALTECC_

DECODER

12

0

8

0

4

1161

29

0

21

0

13

1076

32

0

19

0

12

979

64

0

40

0

27

758

12

2

8

30

19

1188

29

2

20

65

36

1021

32

2

19

71

40

1013

64

2

39

136

79

926

(3)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

5-4

Resource Utilization and Performance

UG-01063

2014.12.19

Altera Corporation

ALTECC (Error Correction Code: Encoder/Decoder)