Vhdl library_use declaration, Ports, Parameters – Altera Integer Arithmetic IP User Manual

Page 28: Vhdl library_use declaration -3, Ports -3, Parameters -3

DENOM : in std_logic_vector(LPM_WIDTHD-1 downto 0);

ACLR : in std_logic := '0';

CLOCK : in std_logic := '0';

CLKEN : in std_logic := '1';

QUOTIENT : out std_logic_vector(LPM_WIDTHN-1 downto 0);

REMAIN : out std_logic_vector(LPM_WIDTHD-1 downto 0));

end component;

VHDL LIBRARY_USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component Declaration.

LIBRARY lpm;

USE lpm.lpm_components.all;

Ports

The following tables list the input and output ports for the LPM_DIVIDE megafunction.

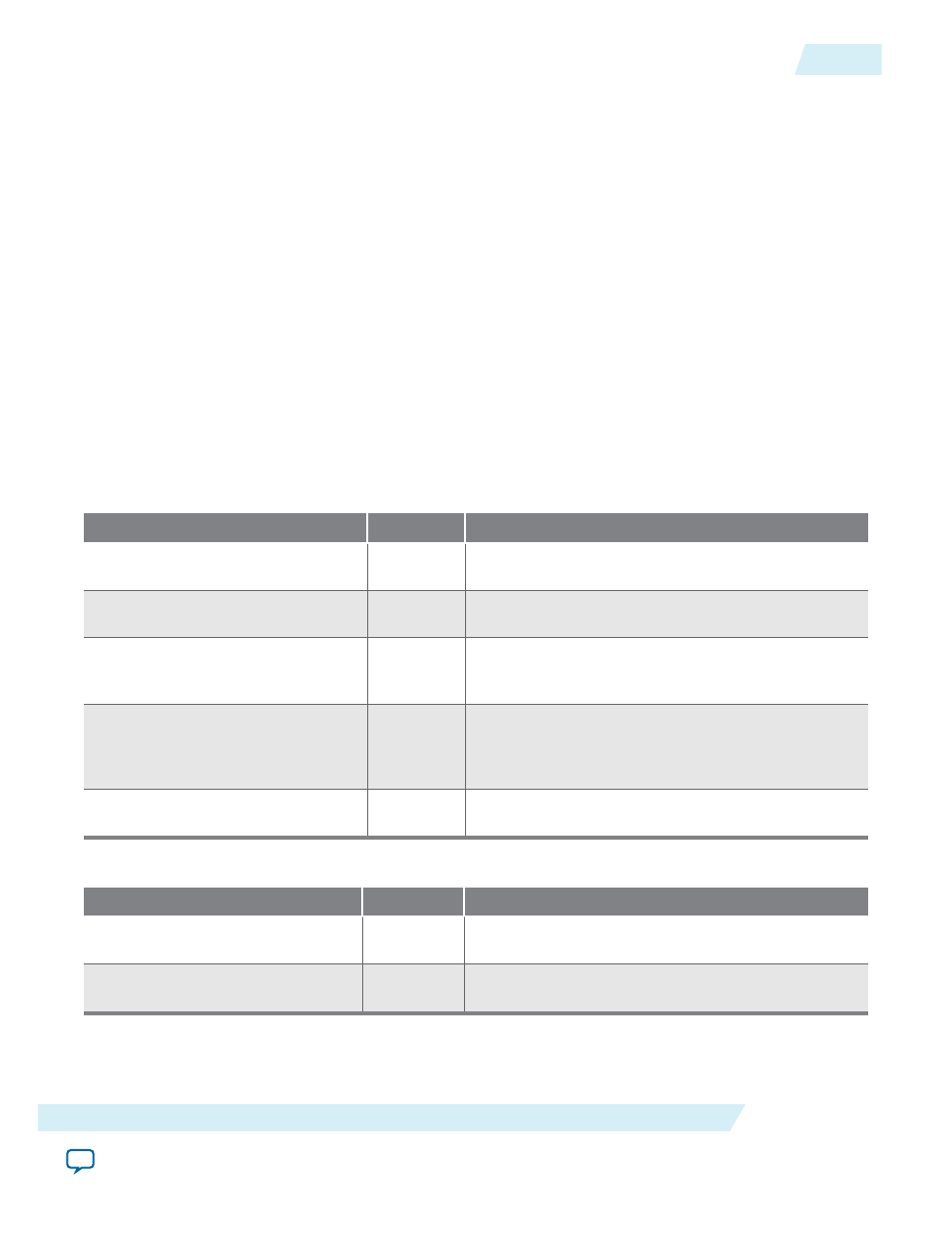

Table 3-2: LPM_DIVIDE Megafunction Input Ports

Port Name

Required

Description

numer[]

Yes

Numerator data input. The size of the input port

depends on the

LPM_WIDTHN

parameter value.

denom[]

Yes

Denominator data input. The size of the input port

depends on the

LPM_WIDTHD

parameter value.

clock

No

Clock input for pipelined usage. For

LPM_PIPELINE

values other than

0

(default), the clock port must be

enabled.

clken

No

Clock enable pipelined usage. When the

clken

port is

asserted high, the division operation takes place.

When the signal is low, no operation occurs. If

omitted, the default value is

1

.

aclr

No

Asynchronous clear port used at any time to reset the

pipeline to all '

0

's asynchronously to the clock input.

Table 3-3: LPM_DIVIDE Megafunction Output Ports

Port Name

Required

Description

quotient[]

Yes

Data output. The size of the output port depends on

the

LPM_WIDTHN

parameter value.

remain[]

Yes

Data output. The size of the output port depends on

the

LPM_WIDTHD

parameter value.

Parameters

UG-01063

2014.12.19

VHDL LIBRARY_USE Declaration

3-3

LPM_DIVIDE (Divider)

Altera Corporation