Altera Integer Arithmetic IP User Manual

Page 53

is needed on the retrieved data F0 (D8D7D6D5D4D3D2D1=1111 0000) based on the generated

syndrome code. Therefore, the flag signals

err_detected

,

err_corrected

, and

err_fatal

are

deasserted, indicating that the data is not corrupted. The decoding for 14F0 is F0 (1111 0000 in

binary).

Note: Even if the generated syndrome code indicates a single-bit error, the

err_detected

and

err_corrected

signals are asserted only if the corrupted bit is from the data bits and not from

the parity bits.

3. At 10 ns, a single-bit error occurred in the input code word that changes the code word to 14F1. In this

case, assume that one of the data bits, the LSB, is corrupted and is inverted from 0 to 1. This causes the

code word to become 14F1.

With the same method of decoding using the Hamming Code scheme, the generated syndrome code is

1 0011. S5* equals to 1 (single error detected), and S4S3S2S1 equals to 0011 (the bit at position 3 is

corrupted).

Because only one of the data bits is corrupted, the decoder is able to correct it by flipping the error bit.

Therefore, the corrupted data F1 is decoded as F0. When F0 is shown at the output port at the next

rising edge of the clock at 17.5 ns, the

err_detected

and

err_corrected

signals are asserted to show

that an error is detected and the single-bit error is corrected.

4. At 20 ns, a double-bit error in the input code word changes the code word to 14F3.

In this case, assume that two of the data bits (bit-0 and bit-1) are corrupted and are inverted from 0 to

1. This causes the code word to become 14F3.

The decoder decodes the code word 14F3 at 20 ns and shows the data F3 at 27.5 ns. The ECC decoder

performs only SECDED, therefore it does not fix the corrupted data that contains double-bit errors.

Instead, the

err_fatal

signal is asserted together with the

err_detected

signal.

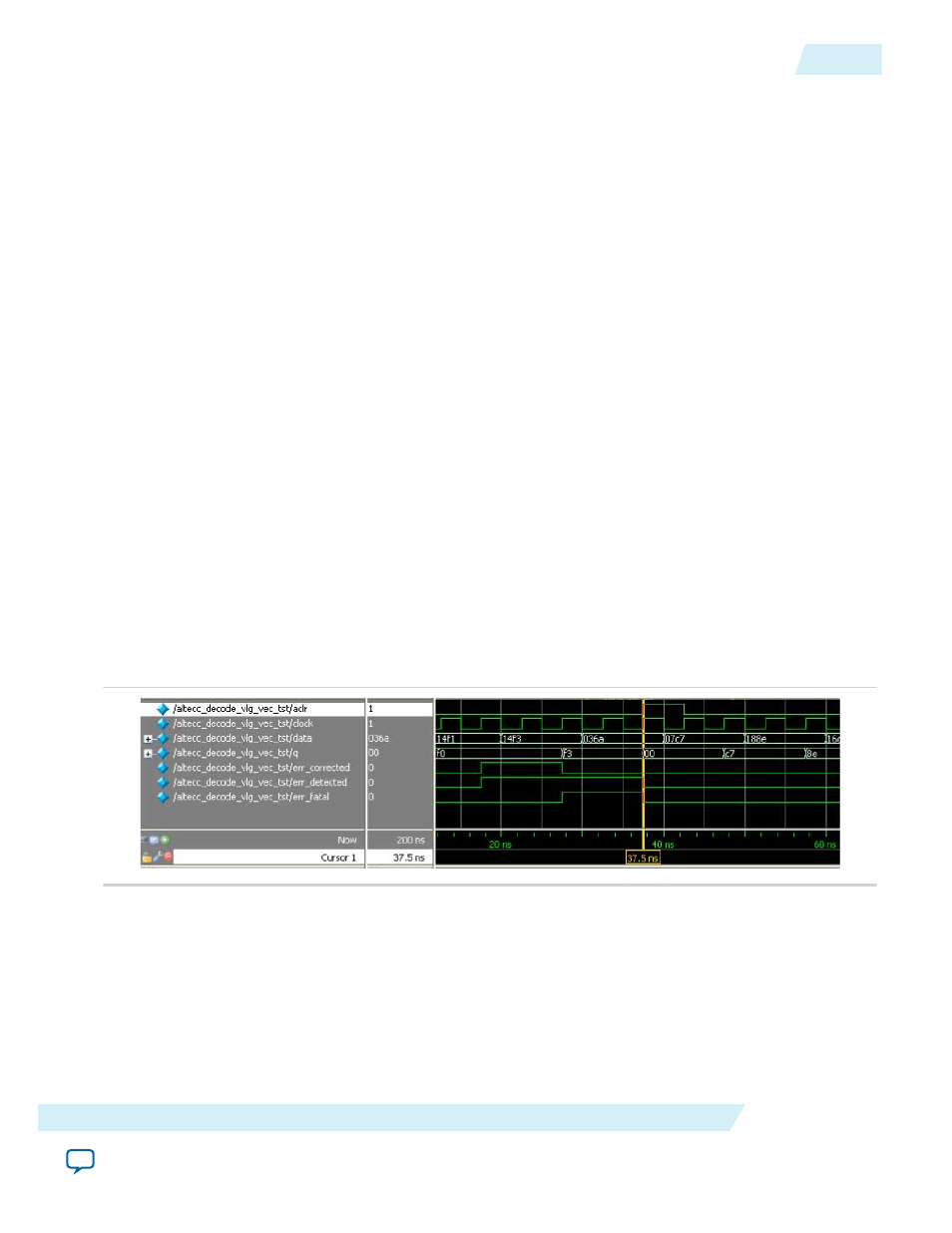

The following figure shows the effects of the asynchronous-clear signal on the registered ports.

Figure 5-7: Design Example 2: Asynchronous-Clear Feature of ECC

This figure shows that when the

aclr

signal is asserted at 37.5 ns, the output and status signals are

cleared immediately.

If you do not want to use the corrupted data when the

err_fatal

signal is asserted, you can assert the

asynchronous-clear signal (

aclr

) to clear the output port q and other status signals that are registered.

You must enable the pipelining option in the MegaWizard Plug-In Manager to use this feature.

UG-01063

2014.12.19

Understanding the Simulation Results

5-15

ALTECC (Error Correction Code: Encoder/Decoder)

Altera Corporation