Altera Integer Arithmetic IP User Manual

Page 84

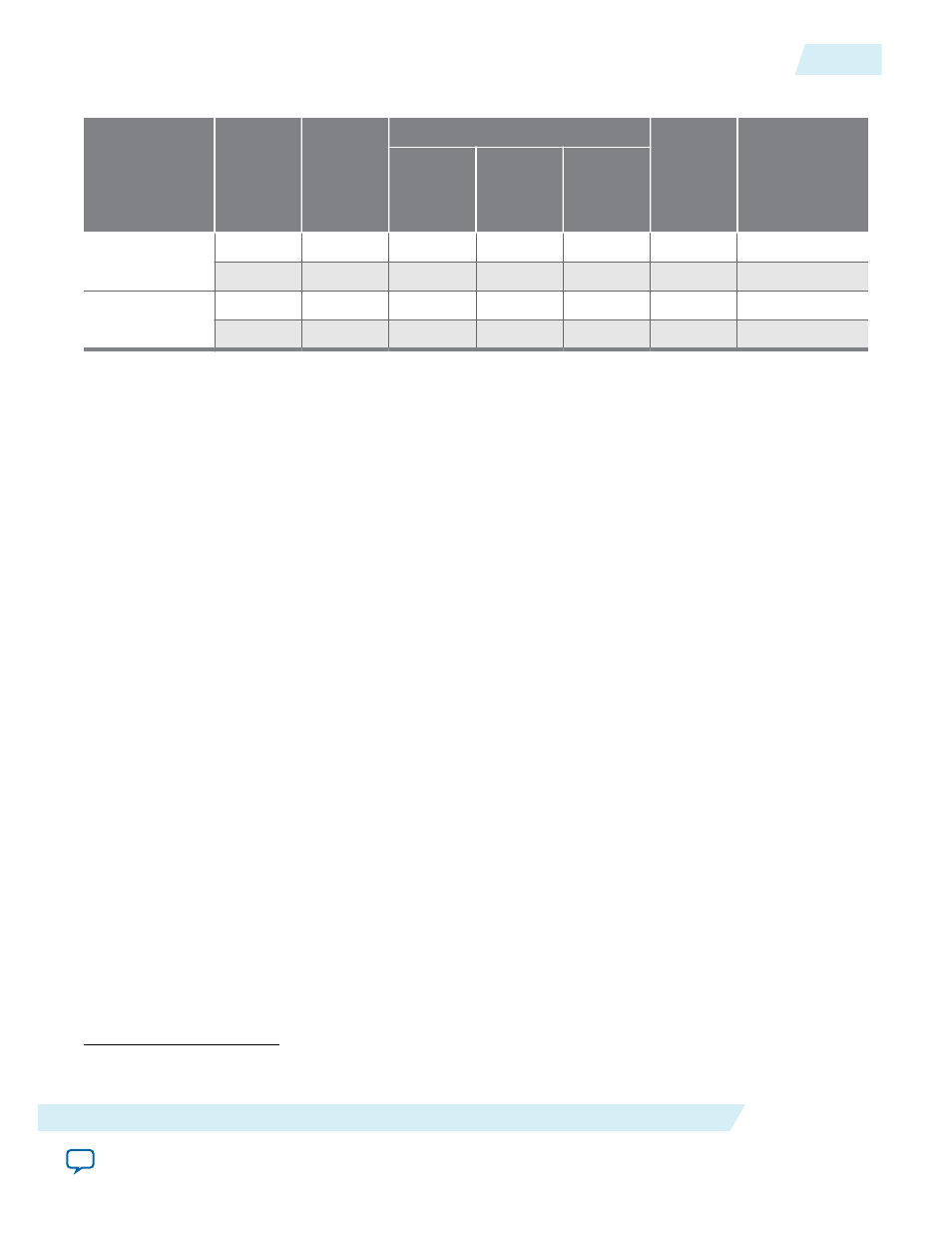

Table 8-1: ALTMULT_ACCUM Resource Utilization and Performance

Device family

Input data

width

Number of

multipliers

Logic Usage

18-bit DSP

f

MAX

(MHz)

(5)

Adaptive

Look-Up

Table

(ALUT)

Dedicated

Logic

Register

(DLR)

Adaptive

Logic

Module

(ALM)

Stratix III

16 ×16

1

0

0

0

4

481

16 ×16

2

0

0

0

4

481

Stratix IV

16 ×16

1

0

0

0

4

443

16 ×16

2

0

0

0

4

443

In the Stratix, Stratix GX, and Arria GX device series, the multiplier and the accumulator of the

ALTMULT_ACCUM megafunction are placed in the DSP block circuitry. For Stratix V devices, the

multiplier blocks and adder/accumulator block (mac_mult and mac_out) are combined into a single

multiplier accumulator (MAC) block. The DSP blocks use the 18-bit × 18-bit input multiplier to process

data with widths of up to 18 bits.

The registers and extra pipeline registers for the following signals are also placed inside the DSP block:

• Data input

• Signed or unsigned select

• Add or subtract select

• Synchronous load

• Products of multipliers

In the case of the output result, the first register is placed in the DSP block. The extra latency registers are

placed in logic elements outside the block.

Cyclone II and Cyclone III devices have embedded multiplier blocks. When the ALTMULT_ACCUM

megafunction is implemented in Cyclone II and Cyclone III devices, the multiplier is implemented in the

embedded multiplier blocks, while the accumulator is put in LEs. In Cyclone devices, both the multiplier

and accumulator are placed in LEs.

For more information about DSP blocks in any of the Stratix, Stratix GX, and Arria GX device series, refer

For more information about the embedded memory blocks in any of the Stratix, Stratix GX, and Arria GX

device series, refer to the TriMatrix Embedded Memory Blocks chapter of the respective handbooks on

the

.

For more information about embedded multiplier blocks in the Cyclone II and Cyclone III devices, refer

For more information about implementing multipliers using DSP and memory blocks in Altera FPGAs,

.

(5)

The performance of the megafunction is dependant on the value of the maximum allowable ceiling f

MAX

that the selected device can achieve. Therefore, results may vary from the numbers stated in this column.

UG-01063

2014.12.19

Resource Utilization and Performance

8-3

ALTMULT_ACCUM (Multiply-Accumulate)

Altera Corporation