Altera Integer Arithmetic IP User Manual

Page 80

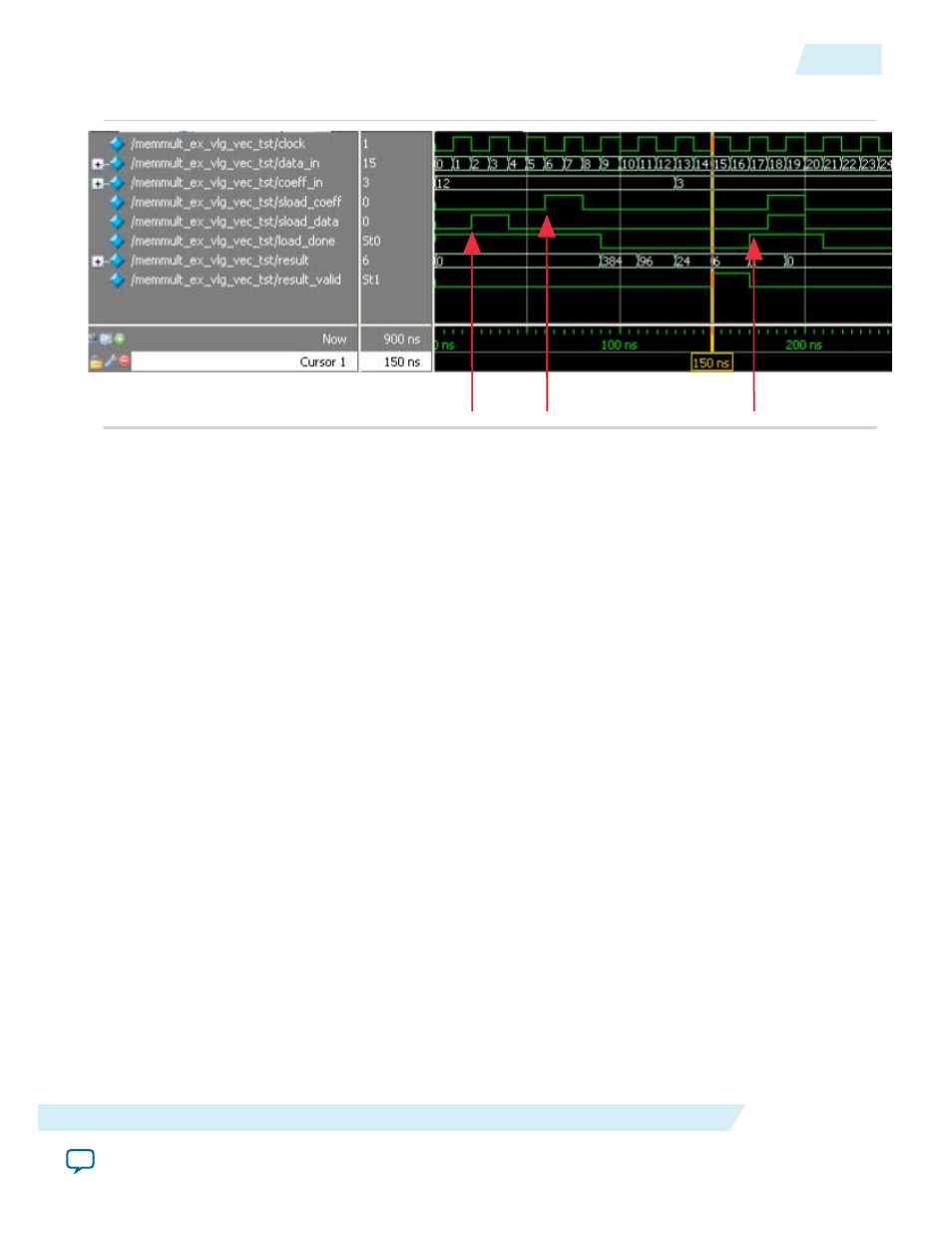

Figure 7-3: Multiplication with Coefficient of 2

The following sequence corresponds with the numbered items in the figure:

1. The following sequence corresponds with the numbered items in the figure:

At 30 ns, the sload_data signal asserts and triggers the first multiplication between the data_in value of

3 and the COEFFICIENT0 value of 2. The result is sent to the result port seven clock cycles later at 150

ns. The result_valid signal asserts to indicate that the multiplication is valid.

2. At 70 ns, the sload_coeff signal asserts to register a new coefficient value of 12 into the register.

3. The load_done signal pulls low to begin loading the new value into the memory, and pulls high at 170

ns when loading is complete. In this example, the load time is five clock cycles.

The following figure shows the simulation results for the multiplication implementation with

coefficient of 3.

UG-01063

2014.12.19

Understanding the Simulation Results

7-7

ALTMEMMULT (Memory-based Constant Coefficient Multiplier)

Altera Corporation