Altera Integer Arithmetic IP User Manual

Page 146

Advertising

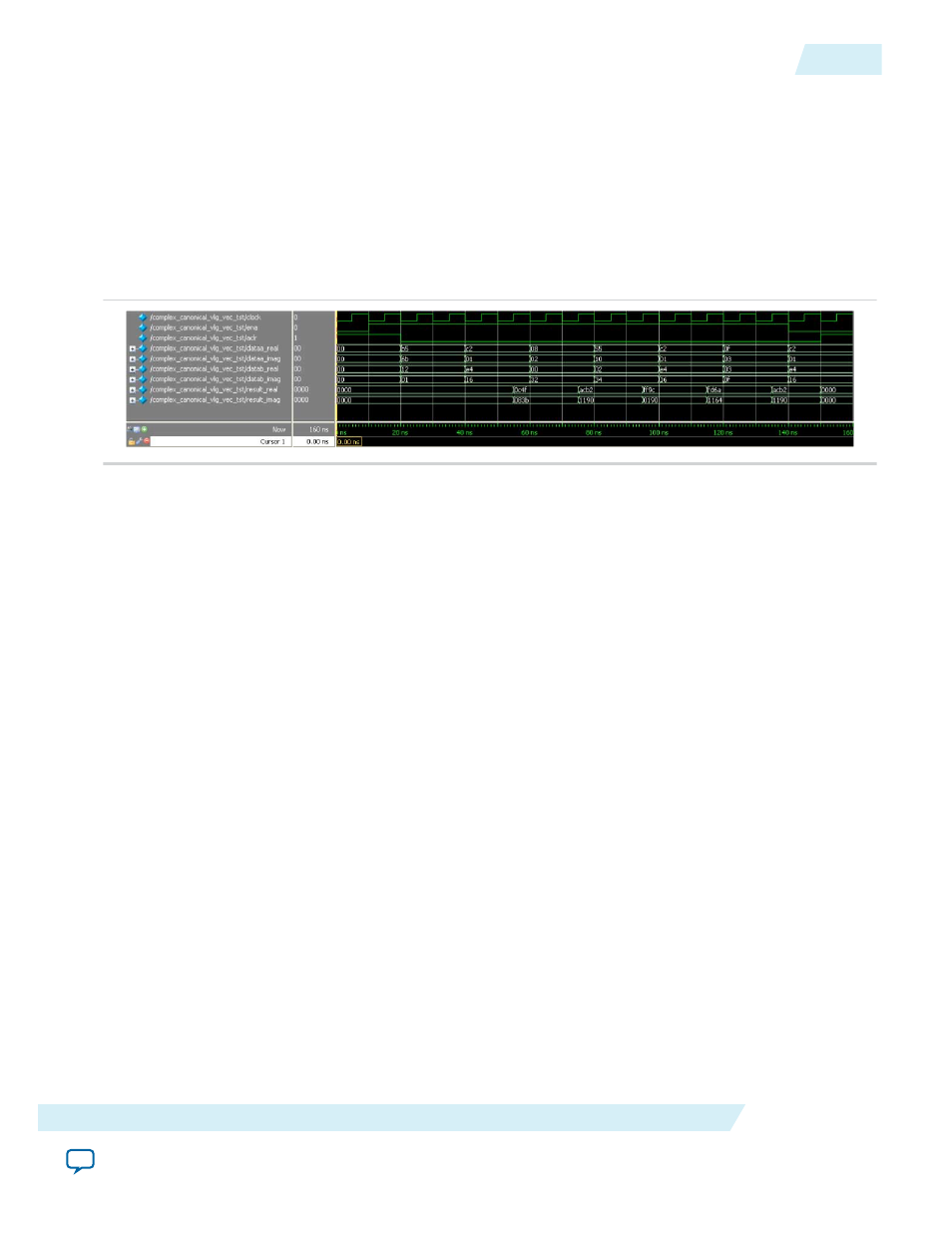

The following settings are observed in this example:

• The widths of the data inputs are all set to 8 bits

• The widths of the output ports are set to 16 bits

• The asynchronous clear (

aclr

) and clock enable (

ena

) signals are enabled

• Pipelining is enabled with an output latency of four clock cycles. Hence, the result is seen on the

output ports four clock cycles after the input data is available

The following figure shows the expected simulation results in the ModelSim-Altera software.

Figure 10-2: ALTMULT_COMPLEX Simulation Results

UG-01063

2014.12.19

Understanding the Simulation Results

10-9

ALTMULT_COMPLEX (Complex Multiplier)

Altera Corporation

Advertising