Altera POS-PHY Level 4 IP Core User Manual

Page 102

6–4

Chapter 6: Testbench

Receiver Testbench Examples

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

1

To simulate errors using these tasks, you must turn on dynamic phase alignment

(DPA) and Atlantic error checking when parameterizing your IP core.

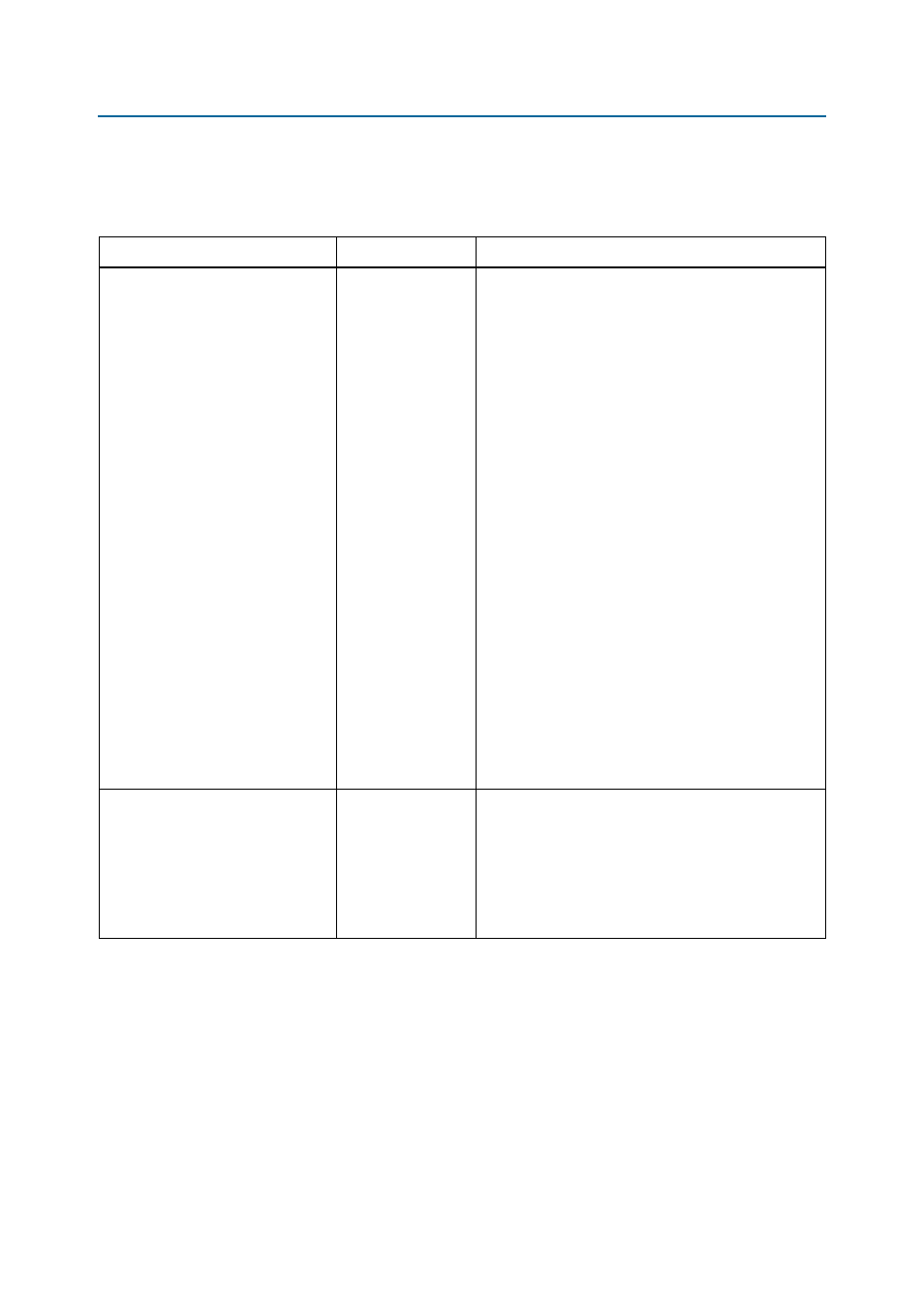

Table 6–3. Error Generation Tasks in the Packet Generation Module

Task Format

General Description

Input Parameters Description

spi_gen.pkt2

(port,err,size,pkt_num)

Sends a single packet

and can optionally

insert various

protocol errors.

port[7:0]

sets the port address (ADR bits [11:4] of SOP

control word).

err

sets the error code for inserting various protocol

errors into the SPI-4 stream. The error codes are:

■

0

= no error

■

1

= invert DIP4 and set error bit

■

2

= omit start of packet (SOP)

■

3

= omit end of packet (EOP)

■

4

= insert a payload control word mid-packet (not really

an error)

■

5

= insert an idle followed by a payload control word

mid-packet (not really an error)

■

6

= set SOP in idle EOP (odd or even) control word

following packet

■

7

= set SOP in idle EOP (abort) control word following

packet

■

8

= set EOP (abort) for packet and insert error bit in

header

■

9

= invert dip4 but do not set error bit

All other values are undefined.

size

sets the length field of the packet header.

pkt_num[7:0]

sets the value of the first byte after the

header. This byte is then incremented for the rest of the

packet.

spi_gen.cw

(word[15:0],dip4err)

Sends a control word

for one clock cycle.

The DIP4 is auto

calculated and

inserted into word

[3:0]. The DIP4

calculation can be

inverted.

word[15:0]

is the control word to be inserted.

When the dip4err bit is set, the DIP4 calculation is

inverted.