Transmitter signals – Altera POS-PHY Level 4 IP Core User Manual

Page 134

G–4

Appendix G: Conversion from v2.2.x

Transmitter Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Transmitter Signals

In the 2.2.x versions of the IP core, data is written to the Atlantic FIFO buffers using

the Atlantic clock (aN_atxclk). The logic, and reading from the Atlantic FIFO buffer, is

synchronous to trefclk/tx_coreclock (transmit clock). The SPI-4.2 transmit clock,

tdclk

, is generated from trefclk. Signals synchronous to trefclk are infixed by _tc_.

The status processor is synchronous to tsclk. Signals synchronous to tsclk are

infixed by _ts_. The external status signals in the shared buffer with embedded

addressing mode are synchronous to the Atlantic clock, a0_txclk.

In the 2.4.x and 2.3.x versions, the logic is synchronous to tdint_clk. The tdint_clk

clock is derived from trefclk. Signals synchronous to tdint_clk are infixed by _td_.

Reading from the Atlantic FIFO buffer is always done using tdint_clk. In the single

clock domain mode, writing to the Atlantic FIFO buffer is synchronous to tdint_clk.

In the multiple clock domain mode, writing to the Atlantic FIFO buffer uses

aN_atxclk

. For more information, refer to the

section of the

“Functional Description—Transmitter”

In 2.4.x and 2.3.x versions of the IP core, the status processor is synchronous to tsclk;

however, the external status signals are in the txsys_clk domain. The txsys_clk clock

is an input to the IP core, and may be set to tsclk. Signals synchronous to tsclk are

infixed by _ts_, and signals synchronous to txsys_clk are infixed by _ty_.

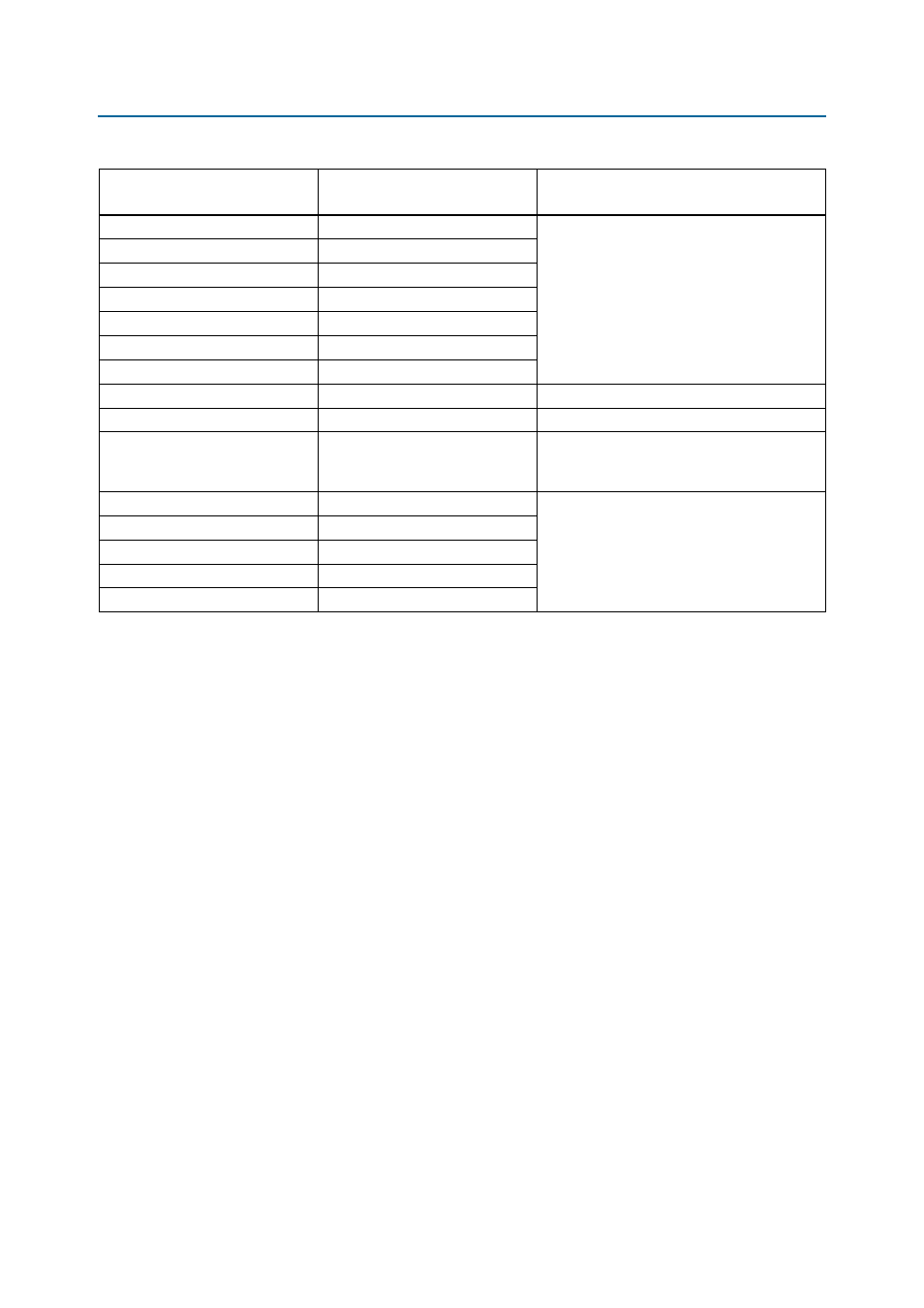

stat_rd_dip4_oos

stat_rr_rx_dip4_oos

No change.

err_rd_dip4

err_rr_dip4

err_rd_pr

err_rr_pr

err_rd_tp

err_rr_tp

err_rd_sob

err_rr_sob

err_rd_sop8

err_rr_sop8

err_rd_eightn

err_rr_eightn

err_rd_abuf_oflw

err_rr_prbuf_oflw

ctl_rd_abuf_flush

ctl_rr_pbuf_flush

err_ry_paddr

err_rr_paddr

In version 2.2.x, this signal is in the rrefclk

domain; in version 2.3.0, this signal is in the

rxsys_clk

domain.

–

err_rr_rxintfifo_oflw

Removed from Signals table.

–

ctl_rr_pbuf_threshold_high

–

ctl_rr_pbuf_threshold_low

–

stat_rr_pbuf_level

–

stat_a0_rxintfifo_empty

Table G–1. Receiver Signal Changes (Part 3 of 3)

Version 2.4.x and 2.3.x Signal

Name

Version 2.2.x Signal Name

Notes