Altera POS-PHY Level 4 IP Core User Manual

Page 133

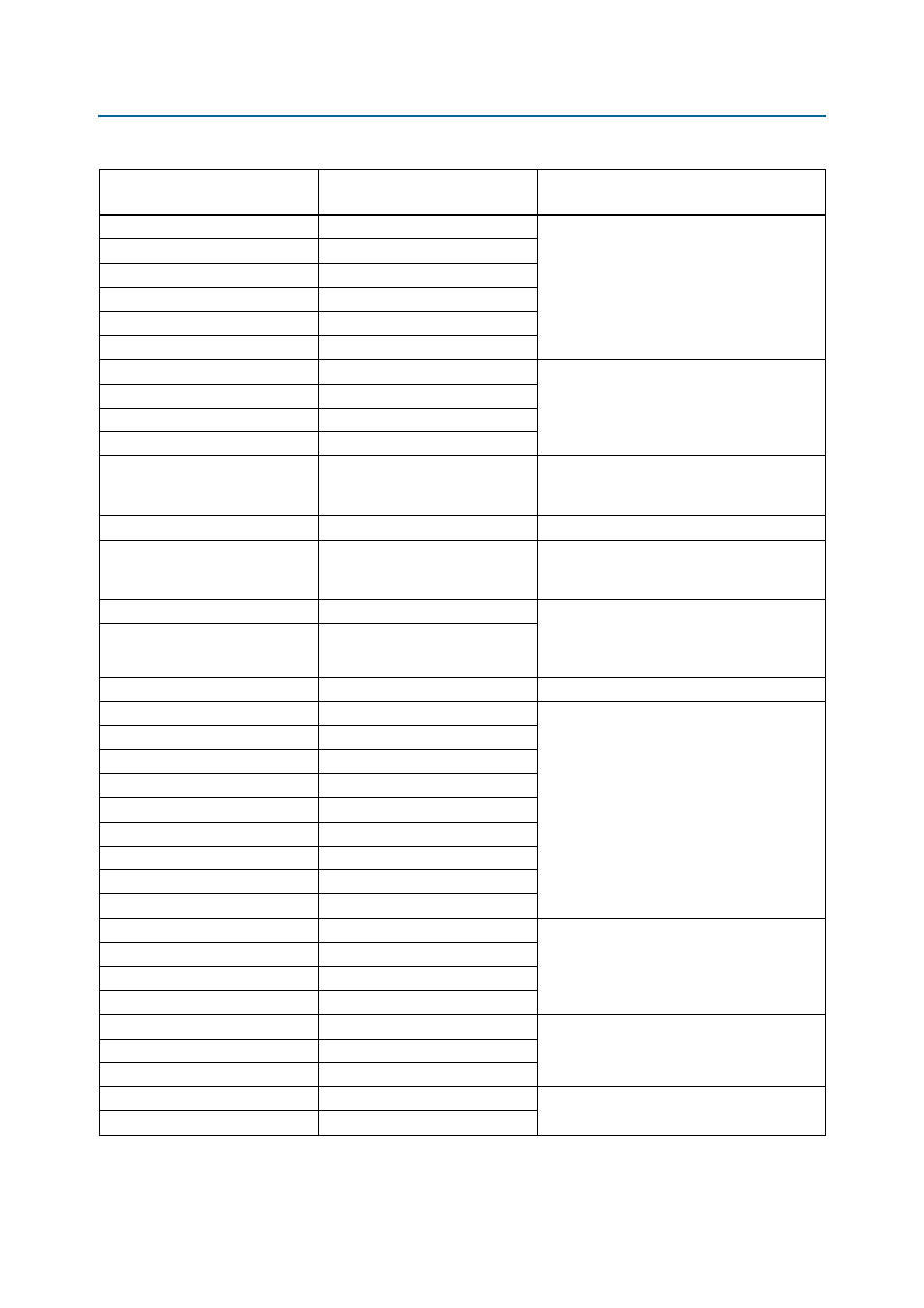

Appendix G: Conversion from v2.2.x

G–3

Receiver Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

err_ry_msopN

err_xx_msop

In version 2.2.x, these signals are in the

rrefclk

domain; in version 2.3.0, these

signals are in the rxsys_clk domain.

err_ry_meopN

err_xx_meop

stat_ry_mp_erradr

stat_xx_mp_erradr

ctl_ry_ae

ctl_xx_rxae

ctl_ry_af

ctl_xx_rxaf

ctl_ry_fifostatoverride

ctl_rr_fifostatoverride

ctl_ry_extstat_val

ctl_a0_extstat_val

No change.

ctl_ry_extstat_adr

ctl_a0_extstat_adr

ctl_ry_extstat

ctl_a0_extstat

ctl_rs_statedge

ctl_rr_statedge

ctl_ry_rsfrm

ctl_rr_rsfrm

In version 2.2.x, these signals are in the

rrefclk

domain; in version 2.3.0, these

signals are in the rxsys_clk domain.

stat_ry_disabled

–

New.

stat_ry_dip2state

stat_rr_dip2state

In version 2.2.x, these signals are in the

rrefclk

domain; in version 2.3.0, these

signals are in the rxsys_clk domain.

ctl_ry_callen

ctl_rr_rxcallen

New restrictions. The system does not function

properly if these signals are set incorrectly.

Refer to

details.

ctl_ry_calm

ctl_rr_rxcalm

stat_ry_calsel

–

New.

rav_clk

–

New Avalon-MM interface signals. These

signals are present only when Asymmetric Port

Support is turned on. rav_reset_n tied high in

the IP Toolbench top-level file.

rav_reset_n

–

rav_address

–

rav_chipselect

–

rav_write

–

rav_read

–

rav_writedata

–

rav_readdata

–

rav_waitrequest

–

err_rd_dpa

err_rr_dpa

No change.

stat_rd_dpa_locked

stat_rr_dpa_locked

stat_rd_dpa_lvds_locked

stat_rr_dpa_lvds_locked

ctl_rd_dpa_force_unlock

ctl_rr_dpa_force_unlock

stat_rd_rdat_sync

stat_rr_rdat_sync

No change.

stat_rd_tp_flag

stat_rr_tp_flag

stat_rd_rsv_cw

stat_rr_rsv_cw

ctl_rd_dip4_bad_threshold

ctl_rr_dip4_bad_threshold

Reduced to 4-bit only.

ctl_rd_dip4_good_threshold

ctl_rr_dip4_good_threshold

Table G–1. Receiver Signal Changes (Part 2 of 3)

Version 2.4.x and 2.3.x Signal

Name

Version 2.2.x Signal Name

Notes