Latency information – Altera POS-PHY Level 4 IP Core User Manual

Page 96

5–26

Chapter 5: Functional Description—Transmitter

Latency Information

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Latency Information

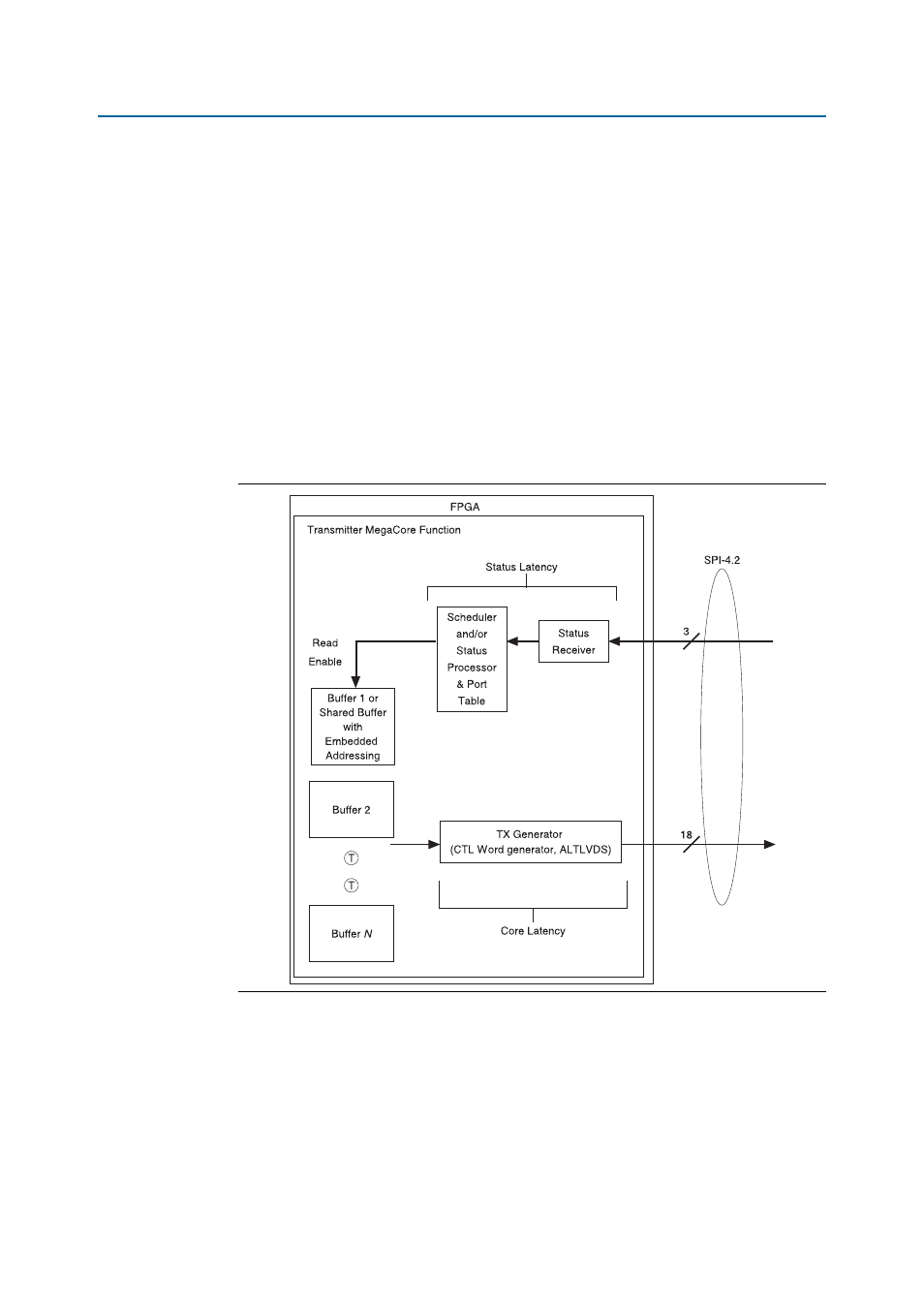

The transmitter IP cores involve two kinds of latency: data latency and status receive

latency.

Data latency is defined as the latency from the Atlantic interface that is reading from

the buffer to the SPI-4.2 LVDS transmit pins. It does not include the latency through

the buffer. For external status, the numbers assume that the aN_atxclk is faster than

the tsclk thus ensuring that the clock-crossing FIFO buffer is empty.

Status receive latency is defined as the latency from the point at which the last cycle of

a valid status message is received (the DIP-2 error code) to the point at which the user

logic or the transmit scheduler can use the status information. It does not include the

time spent waiting for a complete, error-free status message.

Figure 5–12

shows a generic picture of the L

MAX

contributions (transmitter start to

transmitter finish gives the transmitter L

MAX

).

Figure 5–12. L

MAX

Top Level Overview