Altera POS-PHY Level 4 IP Core User Manual

Page 88

5–18

Chapter 5: Functional Description—Transmitter

Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

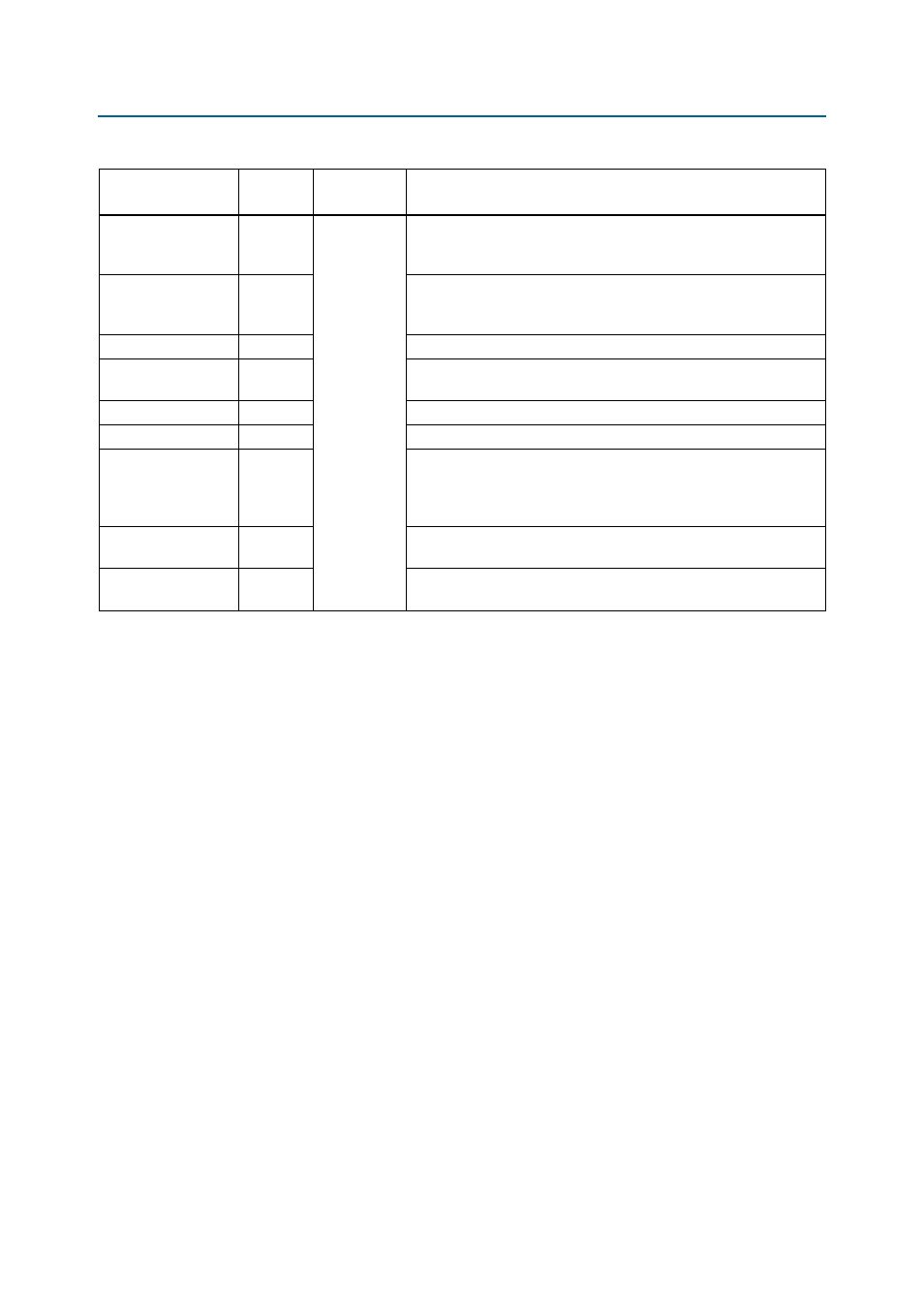

Table 5–5. Atlantic Transmit Interface (Slave Sink)

(Note 1)

Signal

Direction

Clock

Domain

Description

aN_atxclk

Input

aN_atxclk

Atlantic Clock (one for each Atlantic interface). This input is absent

and internally connected to tdint_clk if a single clock domain is

selected. Signals prefixed with aN_ are synchronous to this clock.

aN_atxdav

Output

Atlantic data available (one for each Atlantic interface). Asserted when

the Atlantic FIFO buffer has at least ctl_atx_fth bytes of free space

available.

aN_atxena

Input

Atlantic enable (one for each Atlantic interface).

aN_atxdat[?:0]

Input

Atlantic data bus (one for each Atlantic interface). The width is set by

the Atlantic interface width parameter.

aN_atxsop

Input

Atlantic start of packet (one for each Atlantic interface).

aN_atxeop

Input

Atlantic end of packet (one for each Atlantic interface).

aN_atxmty[?:0]

Input

Atlantic empty signal (one for each Atlantic interface). Number of

invalid octets on the lower bits of aN_atxdat. Valid only when

aN_atxeop

is asserted, must be zero otherwise. The width is

log2(Atlantic interface width/8)

.

aN_atxerr

Input

Atlantic Error (one for each Atlantic interface). Translates to an EOP-

Abort on the transmit data bus.

aN_atxadr[7:0]

Input

Atlantic port address. Only present when you turn on turn on Shared

Buffer with Embedded Addressing.

Note to

Table 5–5

:

(1) N is equal to the number of ports for the individual buffers mode; N is equal to zero when you turn on Shared Buffer with Embedded

Addressing.