Transmitter testbench description – Altera POS-PHY Level 4 IP Core User Manual

Page 104

6–6

Chapter 6: Testbench

Transmitter Testbench Description

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Transmitter Testbench Description

The testbench provided with the transmitter variations of the POS-PHY Level 4 IP

core tests the following functions:

■

Using the Avalon-MM interface, programs the calendar if Asymmetric Port

Support

is turned on (refer to

.)

■

Synchronization of the IP core with a training pattern

■

Data integrity from the Atlantic back-end interface through the user’s

configuration to the SPI-4.2 interface

■

Sends data from multiple ports to the SPI-4.2 interface

■

Verifies that the IP core responds to backpressure on the SPI-4.2 interface (this test

can be turned on and off)

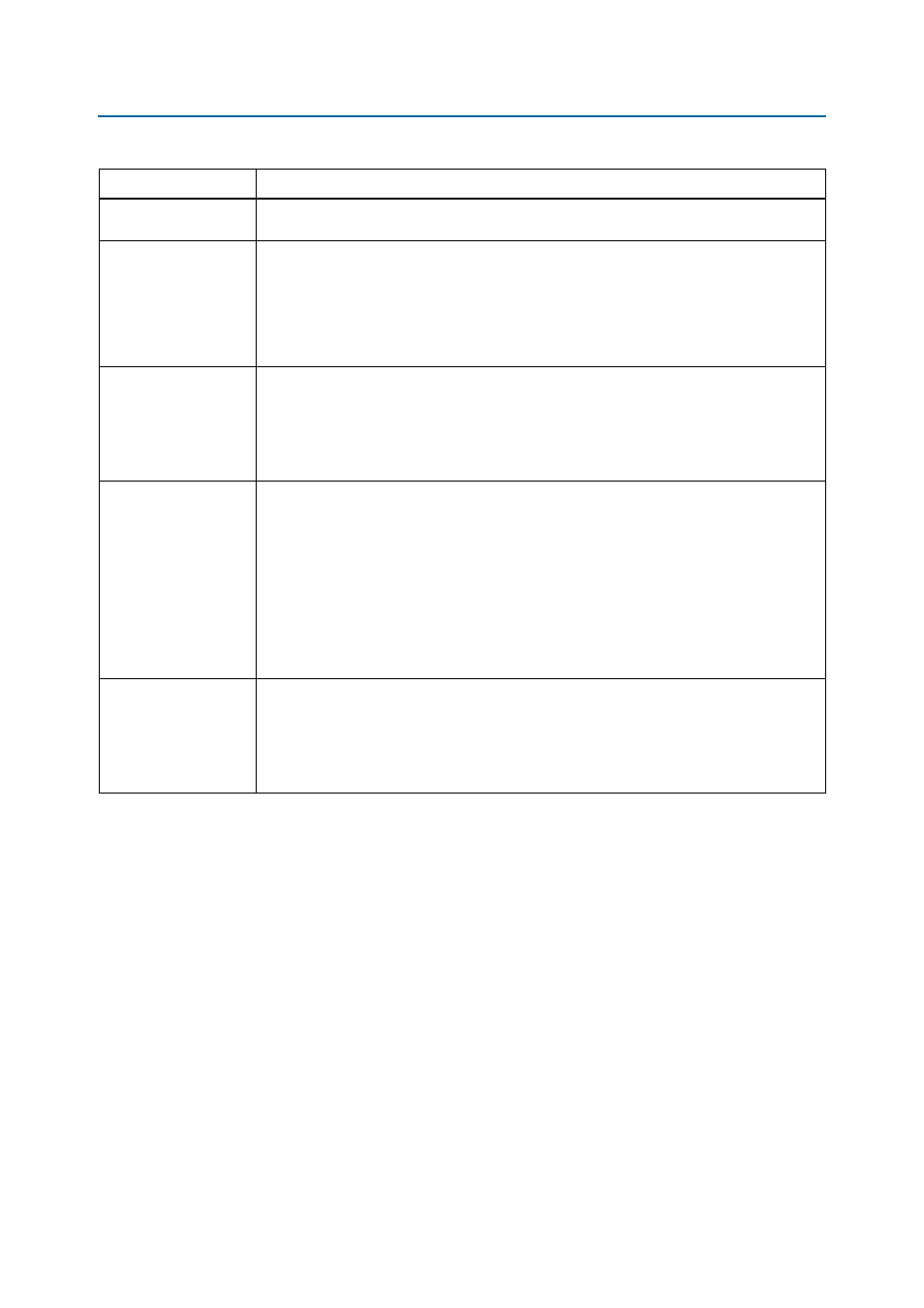

err_rd_dip4

Using the pkt2 task, send in packets with error code 9:

spi_gen.pkt2(

<port>,/*err*/9,<size>,<pkt_num>);

err_rd_pr

This is a catch all error for miscellaneous protocol errors. For example, a payload control word

followed by a payload control word:

spi_gen.cw2(1'b1,1'b00,1'b1,8'h05,1'b0); // Payload control word with SOP

for port 5

spi_gen.cw2(1'b1,1'b00,1'b0,8'h02,1'b0); // Payload control word with

Continue for port 2

err_rd_sob

Send in a data burst that is not properly started, with a payload control word:

spi_gen.cw2(1'b0,1'b00,1'b0,8'h03,1'b0); // Control word without payload

cw bit

set spi_gen.pay(16'h1234);

spi_gen.pay(16'h4567);

err_rd_sop8

Send in packets with SOPs less than 8 cycles apart:

spi_gen.cw2(/*cw_type*/1'b1,/*eop*/2'b00,/*sop*/1'b1,

<port>,/*dip4err*/1'b0

);

spi_gen.pay(16'h1234);

spi_gen.pay(16'h4567);

spi_gen.cw2(/*cw_type*/1'b1,/*eop*/2'b00,/*sop*/1'b1,

<port>,/*dip4err*/1'b0

);

spi_gen.pay(16'h89ab);

spi_gen.pay(16'hcdef);

err_rd_tp

Send in a corrupted training pattern:

repeat (10) spi_gen.cw(16'h0FFF,1'b0); // Send 10 training control word

repeat (99) spi_gen.pay(16'h000F); // Create a tp error with 99 training

data words

Only works after the IP core is aligned with DPA.

Table 6–4. Error Simulation Using the Testbench Module (Part 2 of 2)

Error Signal

Testbench Simulation